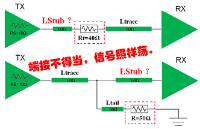

在从事PCB设计之初,我们可能经常会听到这些说法:串联端接电阻需要靠近源端摆放,并联端接电阻需要靠近末端摆放。不明所以的小白就只能直接照做。但在实际项目设计中又可能经常会有困惑,芯片周围已经没有空间了,电阻往外面摆放

2023-02-27 17:29

,断开系统电源,然后再次连接电源以重启系统。本文将探讨使用什么方法和技术可以监控电路的低电平有效输出来驱动高端输入开关,从而执行系统电源循环。

2024-10-30 09:22

在数字电子技术中我们会经常进行高低电平之间的转化,比如说一个模块在接收到信号的时候输出高电平,而另一个元件是低电平触发,如果这两个元器件能够很好配合使用的话,这就必须需要进行电

2022-12-12 09:12

如某宝马轿车的终端电阻,单独装在车头部大灯的下方,一次追尾事故造成这个终端电阻连线断路,而维修师傅不知道其用途,就将它丢弃了。

2018-10-10 10:30

数字信号才是0和1 。凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换,这是由于 3.3V

2017-08-26 16:52

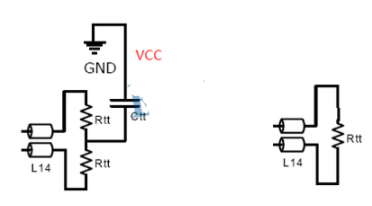

末端并联端接的电阻最好放在接收器之后,走线先连接到接收器,然后拉出一条“尾巴”,端接电阻放在“尾巴”后面,如图所示。

2023-03-22 16:16

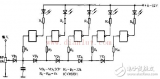

末端并联端接也用的比较多,如前文提到的T点及Fly_by拓扑,其中上拉比较常见,端接电阻通常和传输线阻抗一致。

2021-04-11 09:56

事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线

2018-02-06 12:37

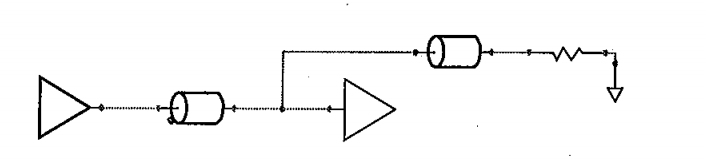

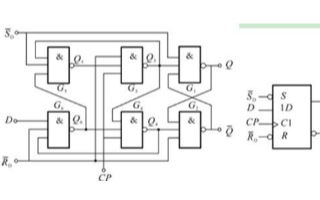

, ZIN是接收器的输入阻抗。 PS:这里仅显示CMOS和PECL/LVPECL电路。 串行端接 实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电

2019-11-11 15:55

3.3V还是5V的TTL的VIH/VIL与VOH/VOL都是一样的,输入的高低电平VIH/VIL一般是2V/0.8V,输出的高低电平VOH/VOL一般是 2.4V/0.4V,也就是 输出:VOH=2.4V;VOL=0

2022-10-27 10:39