CMOS是一种常见的逻辑门电路,它使用CMOS技术来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般

2024-01-09 11:25

CMOS和TTL通过电阻接电源,要如何判断接入高电平还是低电平?

2023-04-25 09:27

电子发烧友网站提供《端接电阻基础知识.doc》资料免费下载

2023-11-21 09:31

”。 1. 数字信号基础 数字信号是电子系统中用来表示信息的电压或电流的变化。在最简单的形式中,数字信号只有两种状态:高电平和低电平。这些状态对应于二进制数字系统中的“1”和“0”。 1.1 高电平

2024-10-17 14:56

端接可以解决很多反射问题,如果还有问题,有没有一种可能是端接电阻阻值没选对?

2024-03-04 15:44

在门电路输入端串联10K电阻后再输入低电平,输入端出呈现的是高电平而不是

2020-08-05 10:41

最近项目在做通过xilinx的ZYNQ控制ADC采样。ADC准备采用ADS5545的CMOS输出模式。我在布板时用Hyperlynx仿真时发现有过冲现象,推荐串联33欧的端接电阻。想问一下在ADC的数据输出引脚需要串联33欧的

2024-12-10 06:24

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判

2024-02-22 11:12

的CMOS电平一般分为逻辑高电平(High Level)和逻辑低电平(Low Level)。CMOS

2024-02-22 11:10

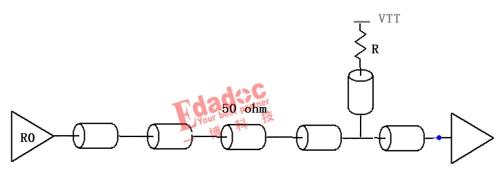

。 VTT为1V时,端接电阻R分别取30ohm,50ohm,70ohm的接收端电压如下图: 可以发现,R与传输线特征阻抗同样都是50ohm时,接收端信号基本没有反射。原因是接收器输入阻抗通常很高,从信号

2024-03-04 15:49