半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判

2024-02-22 11:12

(AHCT与TTL电平兼容) FCT——FACT扩展系列,与TTL电平兼容 FACT——Fairchild Advanced CMOS Technology,其 1,TTL

2018-09-20 18:26

CMOS是一种常见的逻辑门电路,它使用CMOS技术来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般情况下是低

2024-01-09 11:25

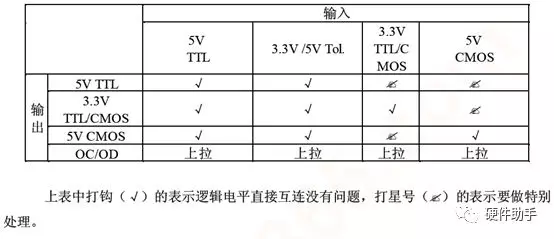

、3.3VTTL、3.3V CMOS、3.3V/5V Tol(输入时3.3V逻辑电平,但是可以接受5V的信号输入)等,随着处理器电压越来越低,现在1.8V

2020-12-23 14:15

TTL电平与CMOS电平的区别 1,TTL电平: 输出高电平>2.4V,输出低

2007-10-10 12:26

晶体管组成了TTL集成电路,TTL大多采用5V电路。用二进制来进行表示的话, 5V正好等于逻辑上的“1”, 0V等于逻辑上的“0”,因此, TTL电平在电路中得以被大星应用。而在此领域中,同样被大量应用的还有CMOS电平

2019-08-19 14:20

数字信号才是0和1 。凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换,这是由于 3.3V

2017-08-26 16:52

CMOS和TTL是两种不同的逻辑电平标准。CMOS(Complementary Metal-Oxide-Semiconductor)和TTL(Transistor-Transistor Logic

2024-02-22 11:10

CMOS集成电路的多余端采取接低电平措施。如果电路的工作速度要求不高,功耗也不需要特别考虑,则可采用多余的输入端和使用端并用的措施加以解决。

2018-09-20 18:20

接口的功耗远低于TTL电平接口。这主要得益于CMOS电路的低静态功耗特性。当电路处于非开关状态时,CMOS电路几乎不消耗能量,从而大大降低了整体功耗。 除了功耗优势外,CMOS

2024-09-30 17:03