在数字电子技术中我们会经常进行高低电平之间的转化,比如说一个模块在接收到信号的时候输出高电平,而另一个元件是低电平触发,如果这两个元器件能够很好配合使用的话,这就必须需要进行电

2022-12-12 09:12

它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。

2018-09-03 16:27

事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线

2018-02-06 12:37

COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,扇出数为10--20个COMS门电路。

2017-08-26 10:02

数字信号才是0和1 。凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换,这是由于 3.3V CMOS 的

2017-08-26 16:52

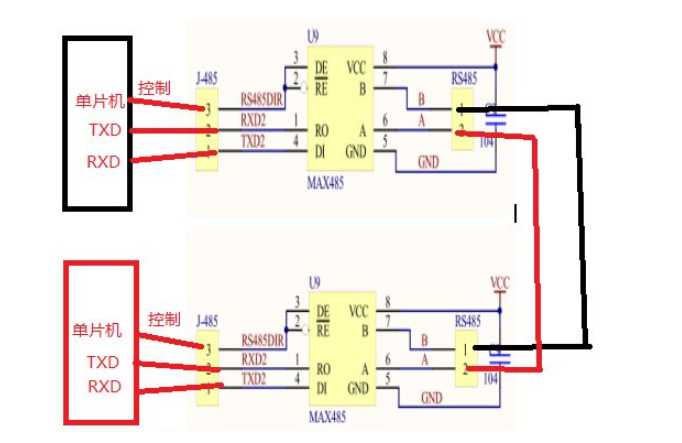

电路设计中,经常遇到各种不相同的逻辑电平。常见的逻辑电平如下: TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS

2022-10-27 10:39

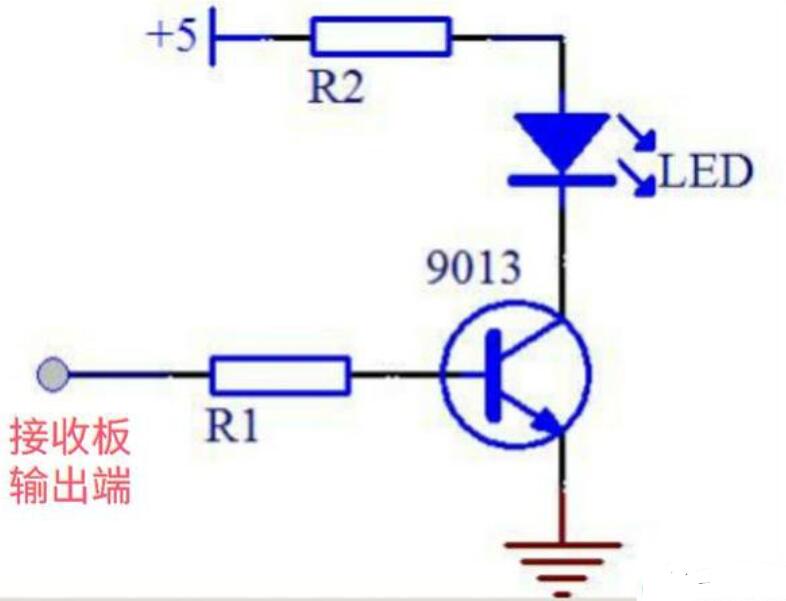

想将一个红外遥控接收板的4个默认输出为低电平的端口改为默认输出为高电平,当接收到红外遥控信号时相应端口输出变为低电平。

2019-11-02 04:00

我们的控制信号出自MCU(5V的系统),而与门的系统供电是12V的,因此两个电平不兼容,导致了MCU的高低电平统一被与门CMOS芯片识别成低电平。

2020-03-15 17:06

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平: 输

2019-09-14 10:52

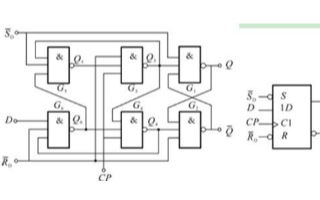

TTL、CMOS电平和OC门知识大全

2018-07-15 10:33