ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在

2017-12-05 09:03

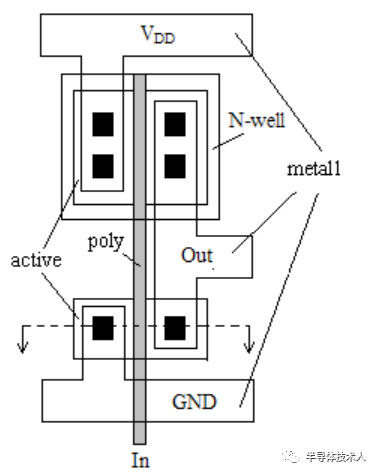

单元电路与版图** ** ·CMOS门电路** ** ·CMOS的功耗表示** 老实说,CMOS比较偏微电子器件,微电子器件还真难...这里我就说一些做数字设计或许要了

2023-01-28 08:16

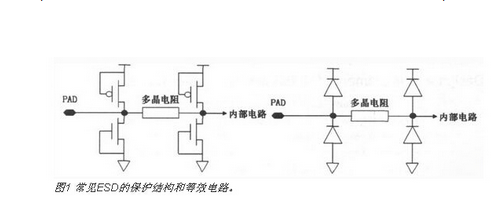

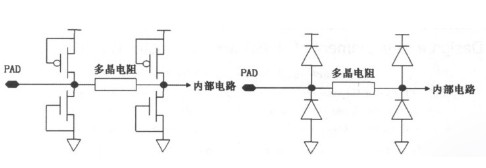

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不

2019-03-04 14:24

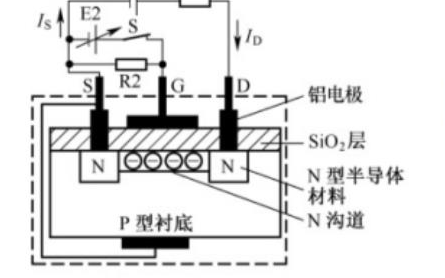

CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。

2023-07-06 14:25

让CMOS集成高压功能,ESD是关口 一个由英飞凌(Infineon Technologies)和印度孟买理工学院(Indian Institute of Technology, Bombay)组成的联合研究小组,近日

2009-05-27 09:26

科技绘梦,心想画成! 商汤日日新大模型旗下图像生成平台“秒画SenseMirage”,帮你开启AI作画之旅。 商汤秒画具备 提示词(Prompt)补全功能 ,结合用户输入少量提示词,即可利用产品

2023-09-14 22:30

CMOS工艺发展到深亚微米阶段,芯片的静电放电(ESD)保护能力受到了更大的限制。因此,需要采取更加有效而且可靠的ESD保护措施。基于改进的SCR器件和STFOD结构,本文提出了一种新颖

2012-03-27 16:27

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不

2019-04-08 15:26

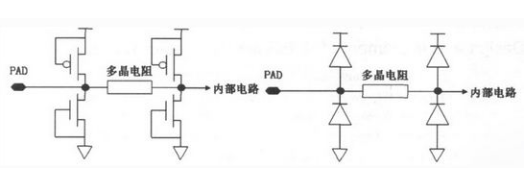

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接

2014-12-24 11:05

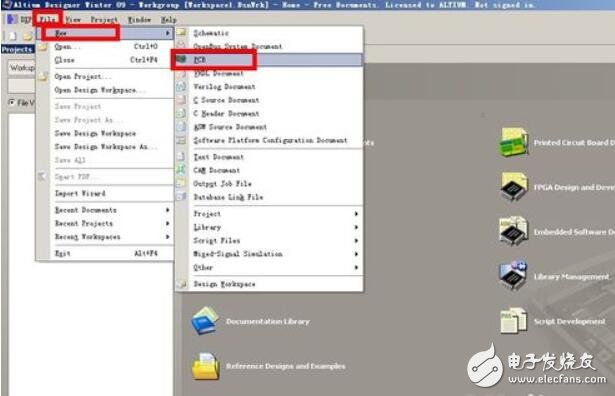

在使用Altium Designer 画PCB时,多数时候画双面板的比较多,但有时抗信号干扰要求更高的情况下,可能会设计四层板或者更多层板,下面以Altium Designer09软件为例,介绍如何画四层板。

2019-05-17 14:42