,输出电压低于VSS+0.5V(VSS为数字地)为逻辑 0。CMOS电路输出高电平约为 0.9Vcc,而输出低电平约为

2019-03-22 07:00

门电路的输出状态,我们需要了解以下几个关键方面: CMOS晶体管的工作原理: N型晶体管(NMOS):在栅极电压高于源极电压时导通,低于源极电压时截止。 P型晶体管(PMOS):在栅极电压低于源极电压时导通,高于源极

2024-07-30 14:52

如题 能否将两个互补输出结构的CMOS门电路输出端并联,接成线与……??我知道TTL的不能但这个不确定……

2012-10-12 23:09

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判

2024-02-22 11:12

CMOS电平:CMOS电路输出高电平为3V~12V,低电平输出接近0V 计算机的MAX232电平:高电平为-5V到-12

2019-09-09 17:26

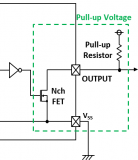

N沟开漏输出、CMOS输出是表示输出端子的输出构成的种类。

2023-09-04 16:09

三极管,CMOS输出是MOSFET。 4、速度和功耗,TTL功耗很大,CMOS功耗随频率增大而增大。 这是TTL和CMOS的几点不同,如果要实现TTL和

2024-01-28 15:38

微控制器主要采用高速CMOS技术制造。信号输入端静态输入电流在1mA左右,输入电容10PF左右,输入阻抗相当高,高速CMOS电路的输出端都有相当的带载能力,即相当大的

2019-09-24 15:22

为了提高数字集成电路芯片的驱动能力,采用优化比例因子的等比缓冲器链方法,通过Hspice软件仿真和版图设计测试,提出了一种基于CSMC 2P2M 0.6 m CMOS工艺的输出缓冲

2012-04-05 15:17