本篇主要针对CMOS电平,详细介绍一下CMOS的闩锁效应。 1、Latch up 闩锁效应是指CMOS

2020-12-23 16:06

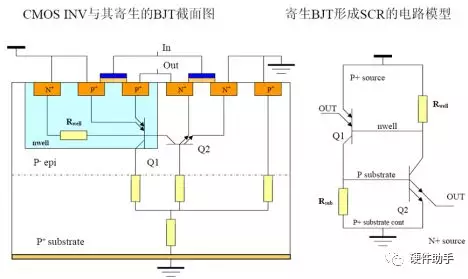

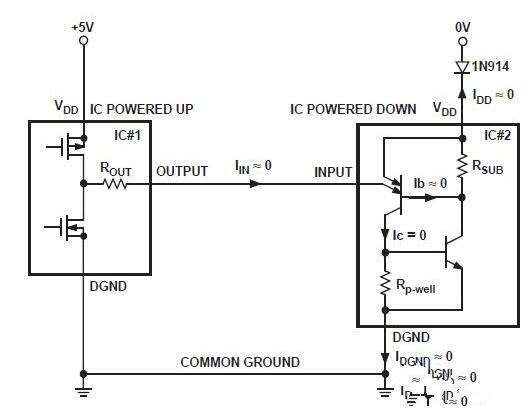

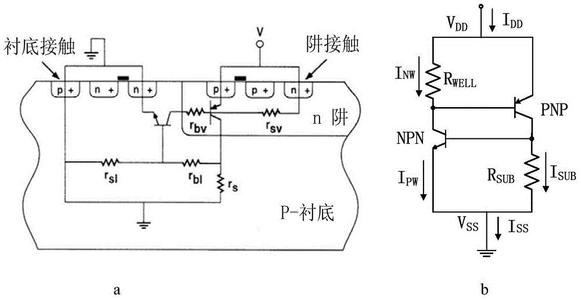

在CMOS电路中,存在寄生的PNP和NPN晶体管,它们相互影响在VDD与GND间产生一低阻通路,形成大电流,烧坏芯片,这就是闩锁效应,简称latch-up。

2025-07-03 16:20

闩锁效应(Latch-up)是CMOS工艺中一种寄生效应,通常发生在CMOS电路

2024-12-27 10:11

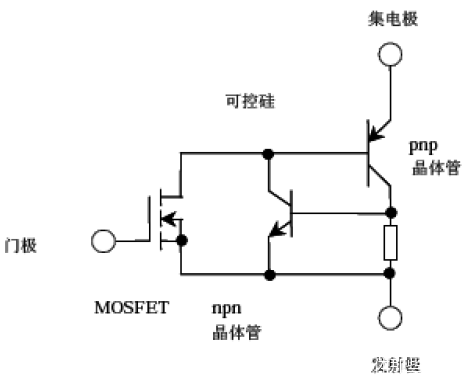

闩锁(Lanch-up)效应,一般我们也可以称之为擎住效应,是由于IGBT超安全工作区域而导致的电流不可控现象,当然,闩锁效应更多的是决定于IGBT芯片本身的构造。实际工作中

2021-02-09 17:05

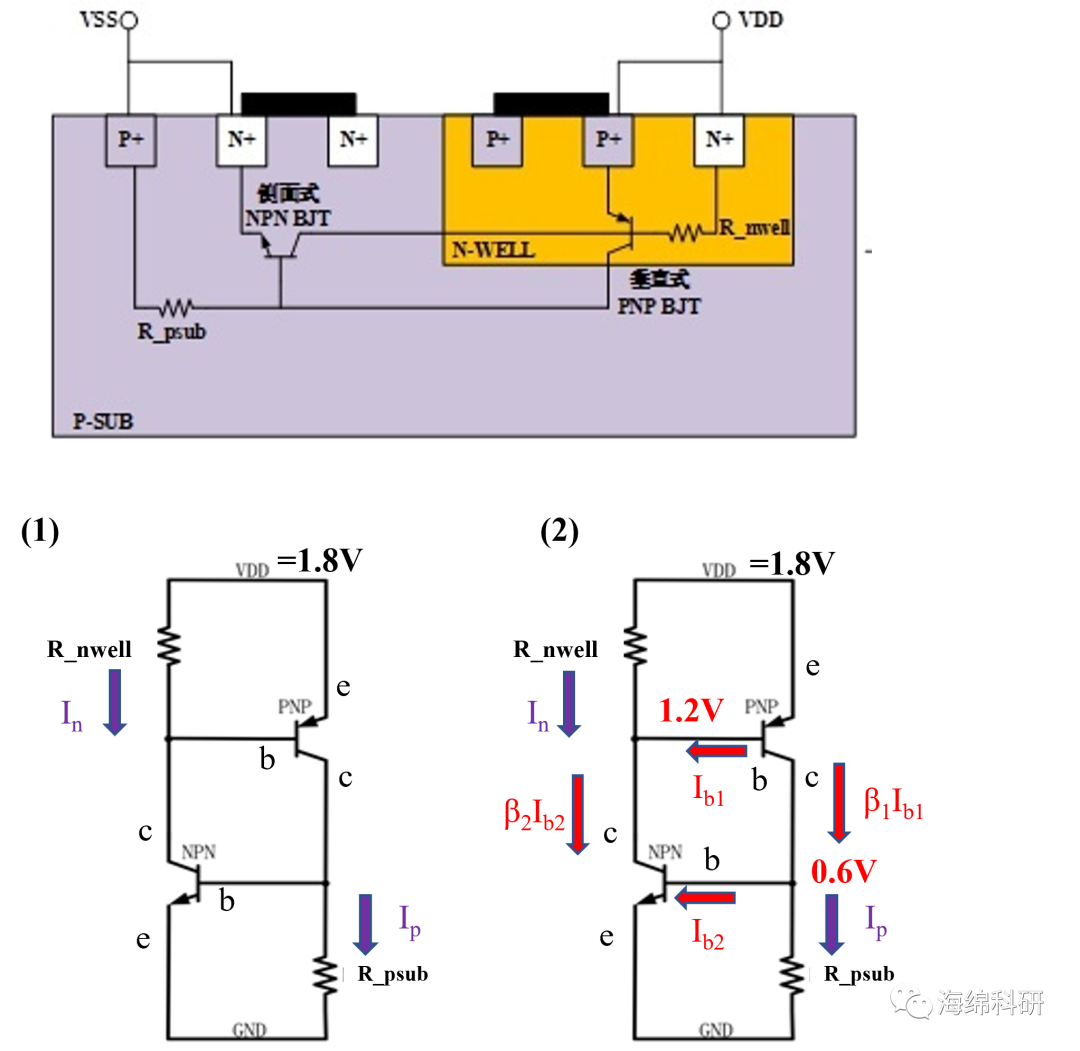

闩锁效应:实际上是由于CMOS电路中基极和集电极相互连接的两个BJT管子(下图中,侧面式NPN和垂直式PNP)的回路放大作用形成的

2023-12-01 14:10

LU是 Latch Up的简写,即闩锁效应,也叫可控硅效应,表征芯片被触发低阻抗通路后、电源VDD到GND之间能承受的最大电流。非车规芯片的规格书中通常都不会提供这个参数,而车规芯片的规格书中通常都会明确标注出来这个参数。这也是一个极为重要却极容易被电子工程师忽略

2025-03-24 17:02

闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。闩锁效应是由NMOS的有源区、P衬底、N阱、

2019-06-11 17:19

闩锁效应,latch up,是个非常重要的问题。现在的芯片设计都不可避免的要考虑它。我今天就简单地梳理一下LUP的一些问题。

2023-12-01 17:11

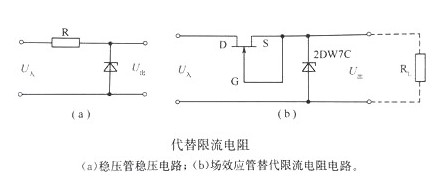

场效应管的应用很广,能够用于调制、放大、阻抗变换、稳流、限流和自动维护等电路中,下面以结场型场效应管为例,扼要引见几种常用的应用

2019-08-29 11:57