CMOS(互补金属氧化物半导体)门电路是数字电子系统中广泛使用的基础构件,因其低功耗、高噪声容限和良好的扩展性而备受青睐。

2024-05-28 16:37

电压探头在测量电路时,通常不建议悬空使用,这主要是由于悬空使用可能导致的一系列问题,包括测量不准确、电路受损风险、以及潜在的安全风险。

2024-05-13 15:04

设计过程中添加的,但最终并未用于电路功能。下面将详细讨论多余输入端的处理方法以及为什么不能悬空使用。 多余输入端的处理方法 1. 短路到接地:这是最常见的处理方法之一。将多余输入端短路到接地,意味着将其与整个

2024-01-16 11:39

单片机引脚悬空是指单片机的I/O引脚在没有连接任何外部电路的情况下,引脚的电平状态。悬空引脚的电平状态取决于单片机的内部结构和外部环境因素。 单片机引脚悬空的电平状态

2024-08-28 09:51

输入端都要加上标准保护电路,但这并不能保证绝对安全,因此使用CMOS集成电路时,必须采取以下预防措施。存放CMOS集成

2018-03-22 15:46

芯片引脚悬空时的电平状态(高电平或低电平)并不是一个固定答案,它取决于多个因素,包括芯片类型、生产厂家、引脚特性以及周围电路环境等。 首先,从逻辑门电路的角度来看,当引脚悬空

2024-08-28 09:55

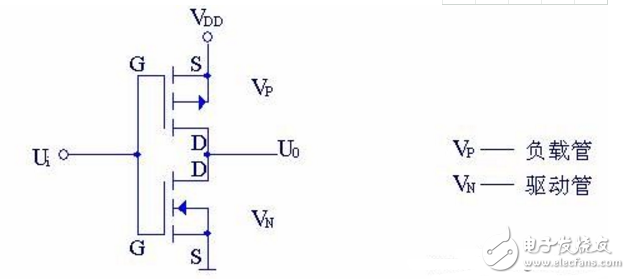

CMOS逻辑电路,CMOS逻辑电路是什么意思 CMOS是单词的首字母缩写,代表互补的金属氧化物半导体(Compleme

2010-03-08 11:31

指针被释放后,是不是就变成了空指针?这是很多刚接触指针的同学存在的误区。

2023-08-17 17:11

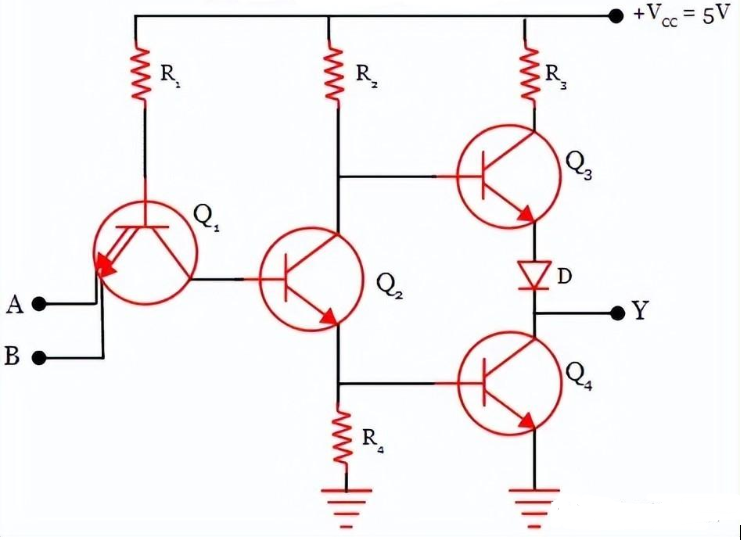

CMOS电路和TTL电路是两种常见的数字电路技术,它们在电路结构、功耗、速度、噪声抗扰能力等方面存在差异。下面是对

2024-02-22 11:06

在TTL电路中,通常会将输入端连接到确定的电平,以确保电路的可靠性。连接到高电平(Vcc)时,表示为逻辑高(1),连接到低电平(地/0V)时,表示为逻辑低(0)。如果输入端悬空,它可能容易受到电磁干扰或漂移,导致

2023-07-26 15:44