你了解CAN总线吗?你知道总线中有哪些错误吗?你想了解总线中的错误是如何校验以及错误之间的关系吗?下文为大家揭开它神秘的面纱。

2018-06-26 10:29

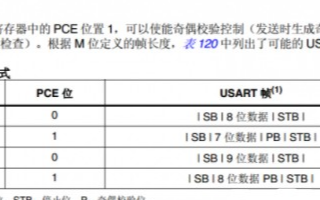

stm32 usart奇偶校验如何配置?或许你在stm32 usart奇偶校验过程中会遇到如下一些坑,stm32 usart偶校验错误标志位以及出现偶

2021-07-23 09:55

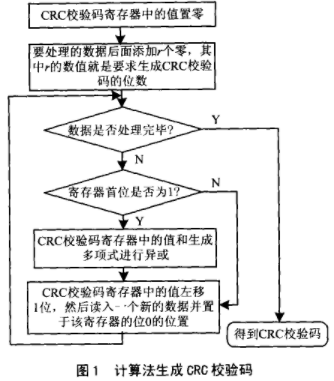

随着技术的不断进步,各种数据通信的应用越来越广泛。由于传输距离、现场状况、干扰等诸多因素的影响,设备之间的通信数据常会发生一些无法预测的错误。为了降低错误所带来的影响,一般在通信时采用数据校验的办法,而循环冗余码

2021-05-05 17:36

VS2005安装后打开程序,提示“包加载失败”的解决办法。首先看看微软Microsoft Software官方给出Fix启动VS环境后提示“包加载失败”的具体操作,原文如下所示

2016-09-26 16:49

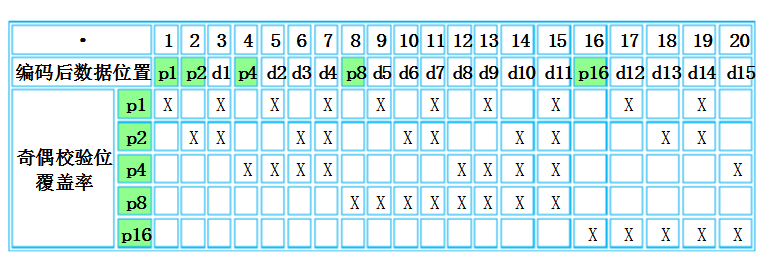

保证存储器中数据的完整性是存储系统设计的一个重要因素。两个主要的方式用于完成这个任务:校验和纠错码(ECC)。传统上,奇偶校验是用的最为常见的手段,但是奇偶校验只有检测一位错误

2019-06-22 10:27

CRC码存储或传送后,在接收方进行校验过程,以判断数据是否有错,若有错则进行纠错。一个CRC码一定能被生成多项式整除,所以在接收方对码字用同样的生成多项式相除,如果余数为0,则码字没有错误;

2023-04-11 09:28

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特),可以计算岀它们的奇偶校验位并与其一起传输。接收端根据接收的数据重新计算其奇偶校验位并与接收的值

2023-09-05 10:40

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12

.简而言之,所有校验位覆盖了数据位置和该校验位位置的二进制与的值不为0的数。 采用奇校验还是偶校验都是可行的。偶校验从数

2018-03-02 15:20

本文的主要内容是校验数字校验字符和特殊需求的常用正则表达式大全

2018-04-30 17:34