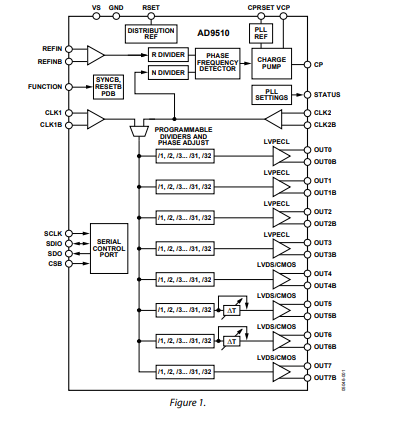

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS

2025-04-15 11:41

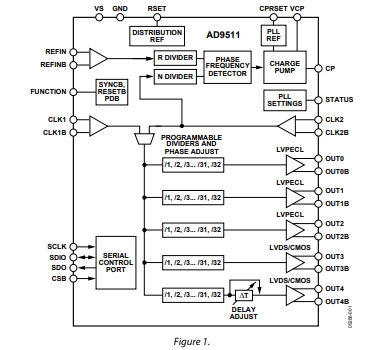

AD9511提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。3路独立的LVPECL时钟输出和2路LVDS

2025-04-15 13:48

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

2018-03-11 10:07

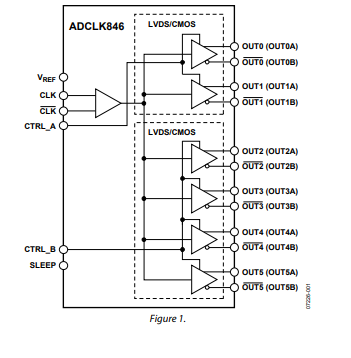

ADCLK846是一款针对低抖动和低功耗优化的1.2 GHz/250 MHz、LVDS/CMOS、扇出缓冲器。可配置范围为6 LVDS至12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线路用于确定固定模

2025-04-11 10:03

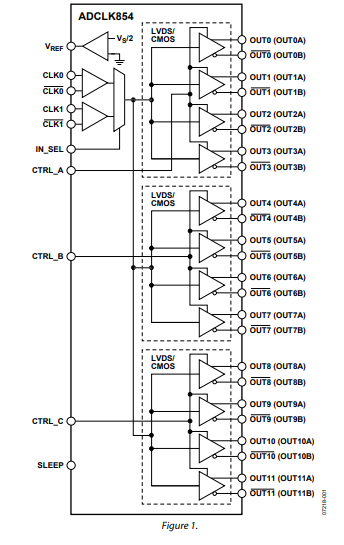

ADCLK854是一款1.2 GHz/250 MHz LVDS/CMOS扇出缓冲器,针对低抖动、低功耗应用进行了优化。其配置范围为12 LVDS至24 CMOS输出,包括LVDS和CMOS输出组合。三条控制线用于确定

2025-04-11 10:48

CCD 和 CMOS 使用相同的光敏材料,因而受光后产生电子的基本原理相同,但是读取过程不同:CCD 是在同步信号和时钟信号的配合下以帧或行的方式转移,整个电路非常复杂,读出速率慢;CMOS 则以类似 DRAM的方式

2017-01-03 11:53

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边

2018-12-06 11:53

CMOS输出是数字电路领域中基于互补金属氧化物半导体技术实现的输出结构类型,其输出电平由输入电压状态直接控制。当输入为高电平时,输出呈现低电平;输入为低电平时则输出高电平 。该技术广泛应用于时钟

2025-08-04 16:21

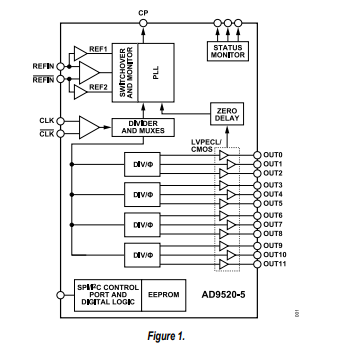

AD9520-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

2025-04-11 11:17

BIOS和CMOS的既相关又不同,BIOS中的系统设置程序是完成CMOS参数设置的手段;CMOS既是BIOS设置系统参数存放场所,又是BIOS设置系统参数的结果。

2018-01-08 19:40