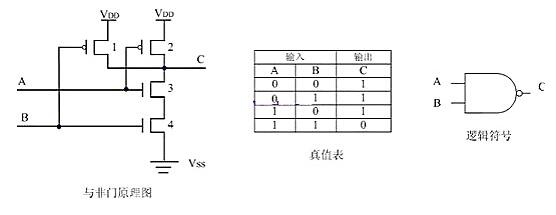

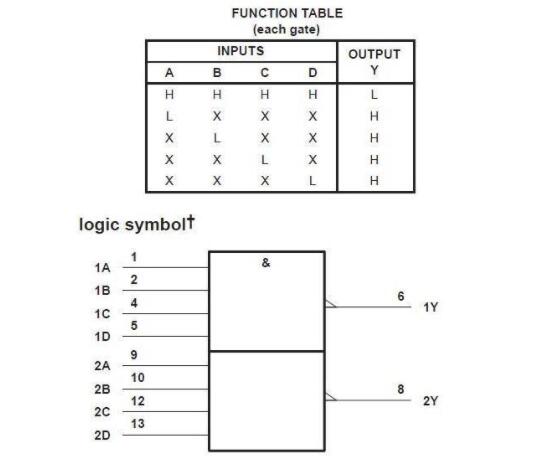

与门真值表和与非门真值表的区别,与门真值表:有0出0,全1出1。与非门真值表

2018-01-30 15:37

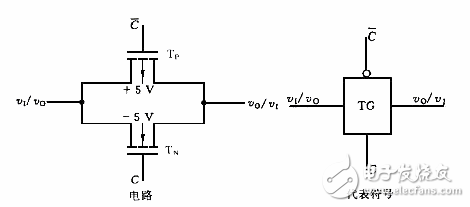

本文主要介绍了cmos传输门如何传输(cmos传输门工作原理及作用_真值表),CMOS传输门(TransmissionGate)是一种既可以传送数字信号又可以传输模拟信

2018-04-08 14:06

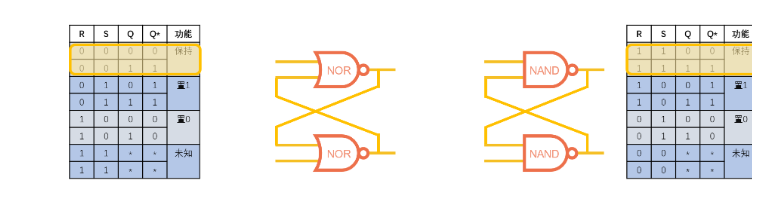

基本的RS触发器是一种使用与非门和或非门构成的存储器元件,它可以存储一个比特的信息并在触发信号的控制下改变状态。与非门和或非门则是用于逻辑运算的基本门电路,它们执行逻辑

2024-03-01 17:22

利用CMOS设计电路需先自行学习NMOS和PMOS的基本原理。

2023-04-11 09:01

与非门(英语:NANDgate)是数字逻辑中实现逻辑与非的逻辑门,功能见左侧真值表。若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1)。与非门是一种通用的逻辑门,因

2019-06-25 14:21

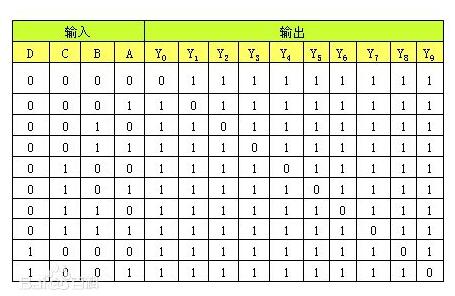

表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

2018-01-30 15:16

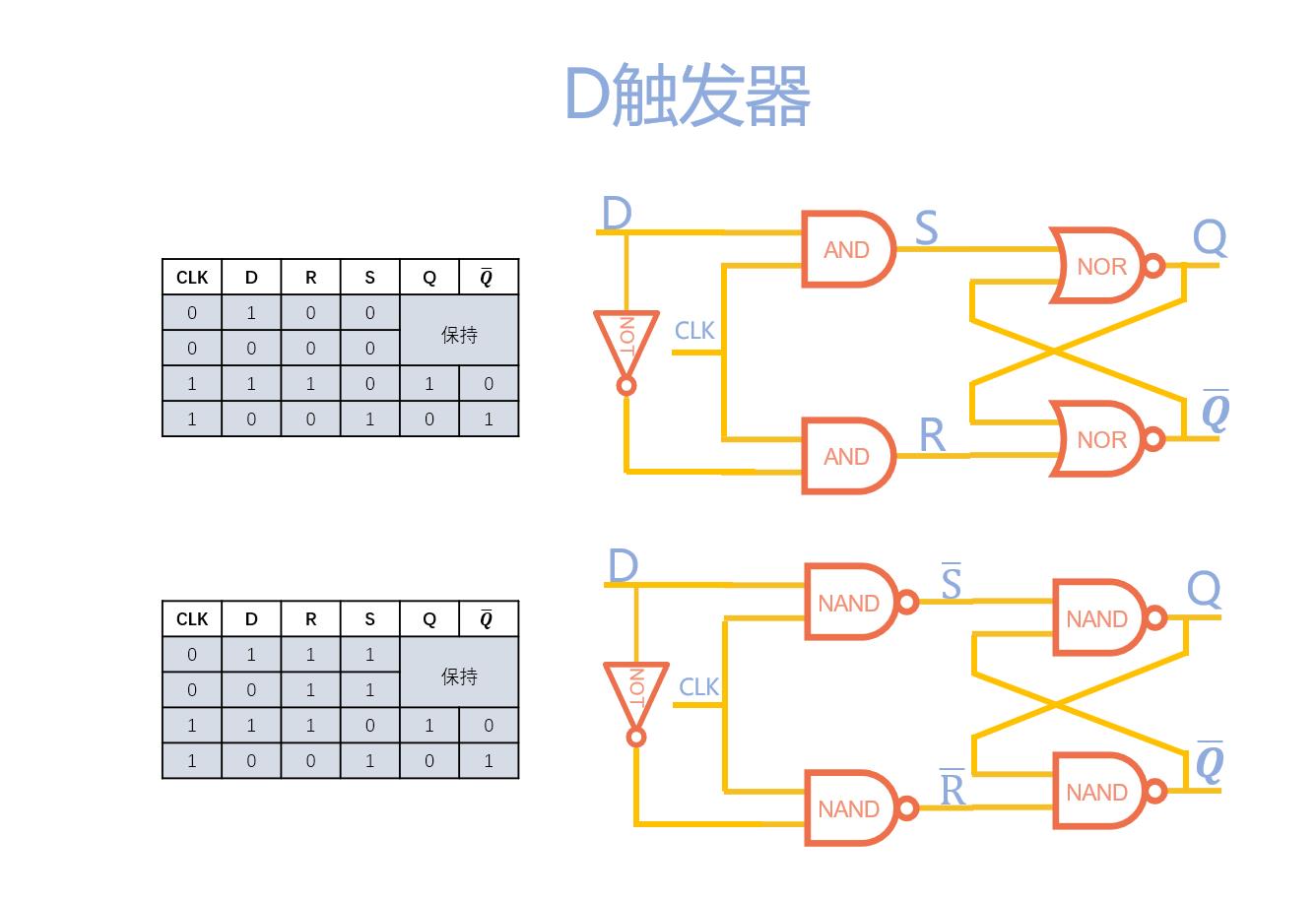

大家好,上次我们研究了D触发器,今天我们继续研究。在开始之前,先来做一点删减,之前我们讨论了用或非门或者与非门实现触发器的方法,在功能上两种实现方法完全相同,在输入输出和实现上略微有些差异。

2023-03-23 13:41

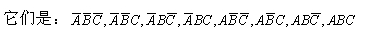

本文主要介绍了逻辑真值表怎么列出的_真值表是怎么画出来的。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个特定的方格图内,此方格图称为卡诺图。由A、B、C三个逻辑变量构成

2018-04-09 11:45

或非门的输出与其输入成反比关系。如果输入信号的电压越高,输出的电压就越低;反之,如果输入信号的电压越低,输出的电压就越高。

2024-02-04 14:31

74ls20是常用的双4输入与非门集成电路,常用在各种数字电路和单片机系统中,其逻辑功能是完成四个输入的逻辑与非计算功能。

2021-06-08 16:09