芯片引脚悬空时的电平状态(高电平或低电平)并不是一个固定答案,它取决于多个因素,包括芯片类型、生产厂家、引脚特性以及周围电路环境等。 首先,从逻辑门电路的角度来看,当引

2024-08-28 09:55

触发器会触发并改变输出状态,这取决于JK触发器的触发方式。 在真实的电路中,JK触发器的触发方式是由实际的电压电平决定的,通常有两种模式,分别是悬空状态为低电平和悬空状

2024-01-15 13:35

请注意LS和CMOS之间的高电平的不兼容性。

2022-03-11 10:28

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判断输出电平的关键是输入电压。在理想的情况下,当输

2024-02-22 11:12

单片机引脚悬空是指单片机的I/O引脚在没有连接任何外部电路的情况下,引脚的电平状态。悬空引脚的电平状态取决于单片机的内部结构和外部环境因素。 单片机引脚

2024-08-28 09:51

TTL电平与CMOS电平的区别 1,TTL电平: 输出高电平>2.4V,输出低

2007-10-10 12:26

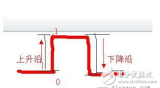

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字电路,电压对应的逻辑电平

2017-11-14 10:37

车载功放的高电平输入 高电平输入是指车载功放可以直接从车载主机接收原本输出至车载扬声器的信

2010-01-04 11:11

(AHCT与TTL电平兼容) FCT——FACT扩展系列,与TTL电平兼容 FACT——Fairchild Advanced CMOS Technology,其 1,TTL

2018-09-20 18:26

在现代电子系统中,数字电路扮演着至关重要的角色。这些电路处理的是二进制信号,即由逻辑“1”和逻辑“0”组成的信号。这些逻辑状态通常通过电压水平来表示,其中高电平代表逻辑“1”,低电平代表逻辑“0

2024-10-17 14:56