芯片引脚悬空时的电平状态(高电平或低电平)并不是一个固定答案,它取决于多个因素,包括芯片类型、生产厂家、引脚特性以及周围电路环境等。 首先,从逻辑门电路的角度来看,当引脚悬空时,其电平状态可能会

2024-08-28 09:55

CMOS(互补金属氧化物半导体)门电路是数字电子系统中广泛使用的基础构件,因其低功耗、高噪声容限和良好的扩展性而备受青睐。

2024-05-28 16:37

触发器会触发并改变输出状态,这取决于JK触发器的触发方式。 在真实的电路中,JK触发器的触发方式是由实际的电压电平决定的,通常有两种模式,分别是悬空状态为低电平和悬空状态为高电平。在本文中,将详细介绍这两种触发方式,并探讨它

2024-01-15 13:35

电压探头在测量电路时,通常不建议悬空使用,这主要是由于悬空使用可能导致的一系列问题,包括测量不准确、电路受损风险、以及潜在的安全风险。

2024-05-13 15:04

单片机引脚悬空是指单片机的I/O引脚在没有连接任何外部电路的情况下,引脚的电平状态。悬空引脚的电平状态取决于单片机的内部结构和外部环境因素。 单片机引脚悬空的电平状态 单片机的I/O引脚在

2024-08-28 09:51

CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0.

2017-08-26 17:26

这款创意台灯底座由铁片构成,足以支撑整个台灯。其独特之处就在于设计师将灯罩与灯座的连接处设计成如油漆低落的感觉,在加上颜色的渲染,远远看去真像是悬空的一个什么东西

2012-07-18 14:57

在电子电路设计中,CMOS(互补金属氧化物半导体)管是一种非常重要的元件,它包括N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS)两种类型。CMOS管的连接方式主要有串联和并联两种

2024-07-30 14:56

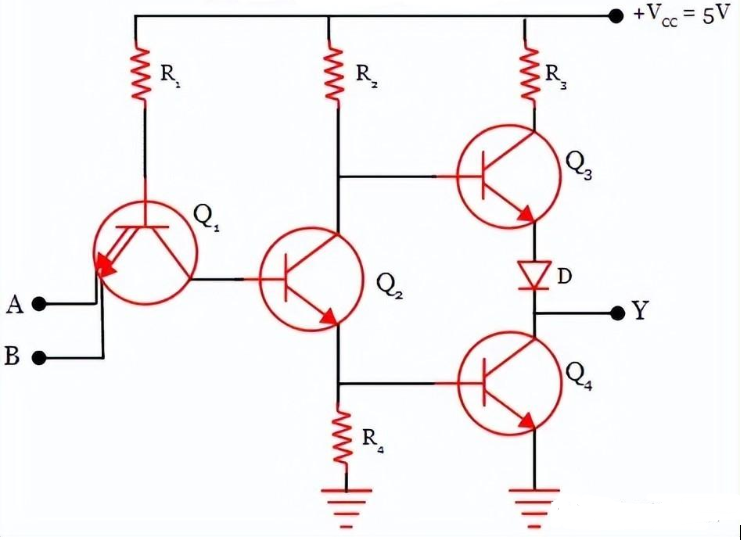

在TTL电路中,通常会将输入端连接到确定的电平,以确保电路的可靠性。连接到高电平(Vcc)时,表示为逻辑高(1),连接到低电平(地/0V)时,表示为逻辑低(0)。如果输入端悬

2023-07-26 15:44

选择CMOS还是sCMOS传感器取决于一系列因素。如果你在两者之间犹豫不决,你很可能使用的是外显照明,因为白光足够亮,不需要sCMOS传感器。

2021-01-22 15:05