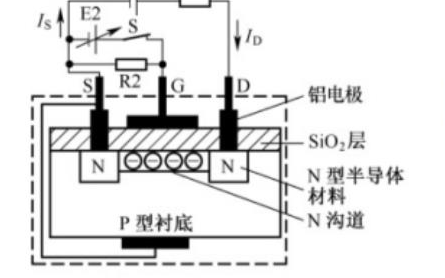

单元电路与版图** ** ·CMOS门电路** ** ·CMOS的功耗表示** 老实说,CMOS比较偏微电子器件,微电子器件还真难...这里我就说一些做数字设计或许要了

2023-01-28 08:16

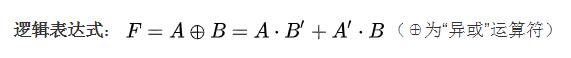

异或门可以用于实现二进制数的加减法。例如,我们可以使用异或门来实现两个二进制数的加法,如果两个相应的输入端上输入的数相同时则进行减法运算。

2024-02-04 14:47

异或门是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入异或门构成。若两个输入的电平相异,则输出为高电平1;

2017-11-28 12:07

本文章主要详细介绍了pcb版图设计工具,分别有FreePCB、MentorPADS、MentorWG2005。

2019-04-24 17:47

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入

2020-11-19 16:06

版图将会对模拟电路性能产生巨大的影响,针对matching要求很低,nmos的body-effect不可小视,current matching即使差到20%~40%,matching最后造成了接近50%的偏差,也就是差不多到了1:600。

2018-02-16 10:02

PCB最佳设计方法是将PCB原理图传递给版图(layout)设计时需要考虑的六件事。本文中提到的所有例子都是用Multisim设计环境开发的,不过在使用不同的EDA工具时相同的概念同样适用,工程师

2016-11-04 19:26

近日,法动科技联合杭州电子科技大学陈世昌教授科研团队,成功开发出基于人工智能技术的版图级优化设计流程,有效改善高频电路版图设计自动化程度低的现状,提升功率放大器性能和设计效率。

2022-09-15 11:11

在集成电路设计中,版图(Layout)是芯片设计的核心之一,通常是指芯片电路的物理实现图。它描述了电路中所有元器件(如晶体管、电阻、电容等)及其连接方式在硅片上的具体布局。版图是将电路设计转化为实际

2025-04-02 14:07

通过网表文件将原理图传递到版图环境的过程中还会传递器件信息、网表、版图信息和初始的走线宽度设置。

2018-04-25 14:10