ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD

2017-12-05 09:03

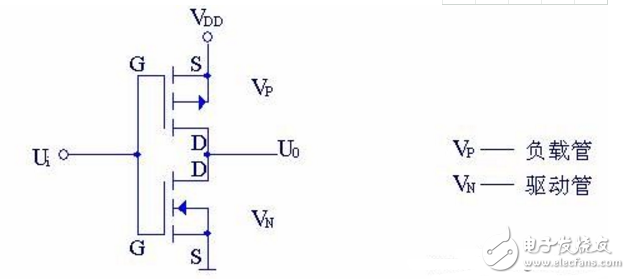

本文设计了一种CMOS工艺下的欠压保护电路,首先分析了电路的工作原理,而后给出了各MOS管的参数计算,并给出pspice仿真的结果。此

2014-08-14 15:03

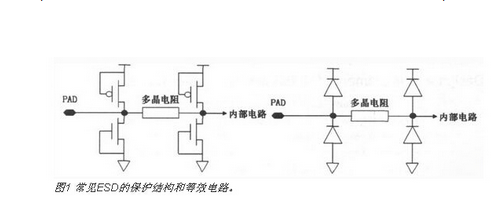

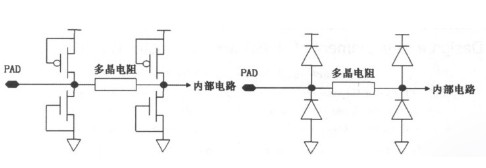

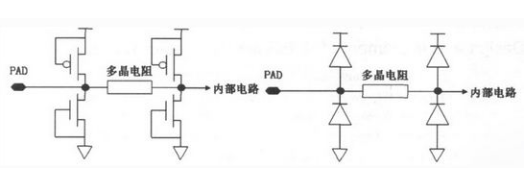

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作

2019-03-04 14:24

CMOS(互补金属氧化物半导体)集成电路是一种广泛使用的半导体技术,用于构建各种电子电路和集成电路。

2024-05-28 15:32

一则CMOS电路设计问题 这次遇到的问题是这样的,由于LDO的电源输出能力有限,同时也是保证可靠性,某些保护电路必须直接电源上,这里需要注释

2009-11-21 15:05

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作

2019-04-08 15:26

输入端都要加上标准保护电路,但这并不能保证绝对安全,因此使用CMOS集成电路时,必须采取以下预防措施。存放CMOS集成

2018-03-22 15:46

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接

2014-12-24 11:05

使用时的技术要求 1.CMOS集成电路输入端的要求 CMOS集成电路具有很高的输入阻抗,其内部输入端接有二极管

2018-09-20 18:20

CMOS集成电路具有很高的输入阻抗,其内部输入端接有二极管保护电路.以防范外界干扰、冲击和静电击穿。

2012-04-01 11:00