摘要: 本文设计了一种CMOS工艺下的欠压保护电路,首先分析了电路的工作原理,而后给出了各MOS管的参数计算,并给出pspice仿真的结果。此

2018-08-27 15:54

CMOS工艺锂电池保护电路图的实现

2012-08-06 11:06

摘要:静电放电(ESD)对CMOS电路的可靠性构成了很大威胁。随着CMOS电路集成度的不断提高,其对ESD保护的要求也更

2010-05-11 08:53

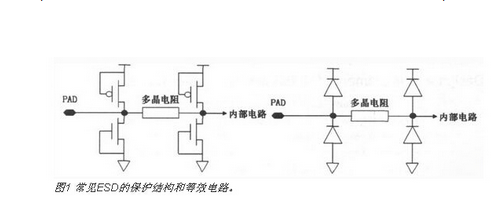

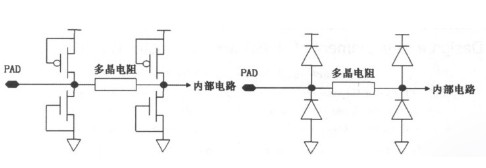

本文研究了在CMOS 工艺中I/O 电路的 ESD 保护结构设计以及相关版图的要求,其中重点讨论了PAD 到VSS 电流通路的建立。关键词:ESD 保护

2009-12-14 10:45

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD

2017-12-05 09:03

本文设计了一种CMOS工艺下的欠压保护电路,首先分析了电路的工作原理,而后给出了各MOS管的参数计算,并给出pspice仿真的结果。此

2014-08-14 15:03

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作

2019-03-04 14:24

高速CMOS 电路的操作保护措施 静电放电(ESD)是CMOS电路失效的原因之一。所谓静电放电是指:不同静电电位(由于直

2017-11-23 15:34

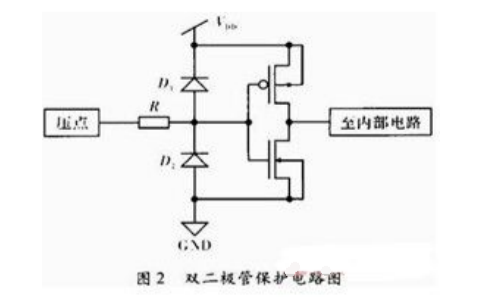

1 . GMOS 集成电路输入端的要求 CMOS 集成电路具有很高的输入阻抗,其内部输入端接有二极管保护电路,以防范外界

2018-12-13 09:47

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越

2020-12-30 10:28