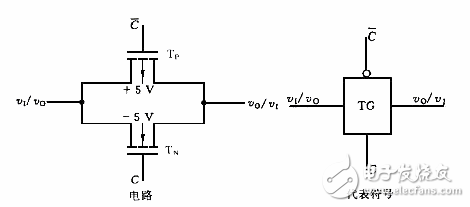

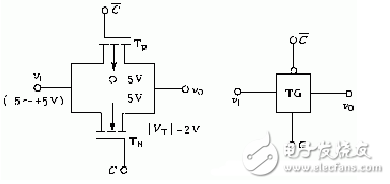

本文主要介绍了cmos传输门如何传输(cmos传输

2018-04-08 14:06

与门真值表和与非门真值表的区别,与门真值表:有0出0,全1出1。与非门真值表:有0出1,全1出0。

2018-01-30 15:37

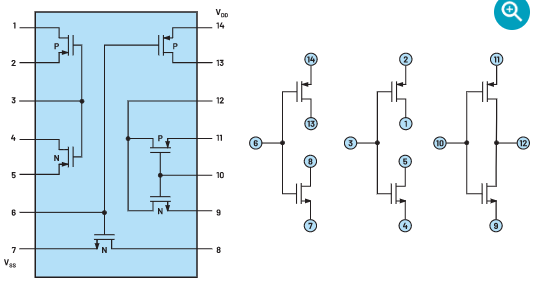

本实验活动的目标是进一步强化上一个实验活动 “使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而

2023-05-29 14:17

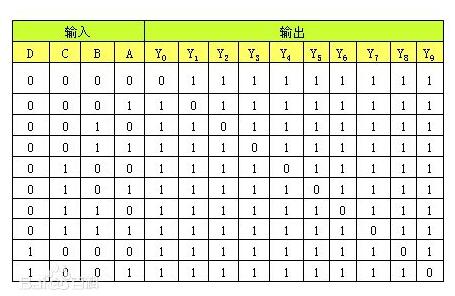

表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

2018-01-30 15:16

本文主要介绍了cmos传输门芯片型号有哪些?重点介绍了四联双向开关CC4016cmos传输

2018-04-08 14:27

本文主要介绍了逻辑真值表怎么列出的_真值表是怎么画出来的。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个特定的方格图内,此方格图称为卡诺图。由A、B、C三个逻辑变量构成

2018-04-09 11:45

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进行级联可以得到多位。全加器是形成三位算术和的组合电路,它由三个输入和两个输出组成。

2021-06-29 09:14

半加器、全加器是组合电路中的基本元器件,也是CPU中处理加法运算的核心,理解、掌握并熟练应用是硬件课程的最基本要求。

2018-07-25 14:39

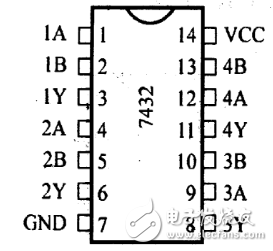

本文主要介绍了74ls32引脚图及功能真值表和特性参数。74LS32器件包含4路独立的2输入或门。74LS32的逻辑功能表达式为:Y=/(A·B)或Y=A+B,正逻辑。引出端符号:1A-4A 输入端、1B-4B 输入端、1Y-4Y 输出端。

2018-04-09 14:37

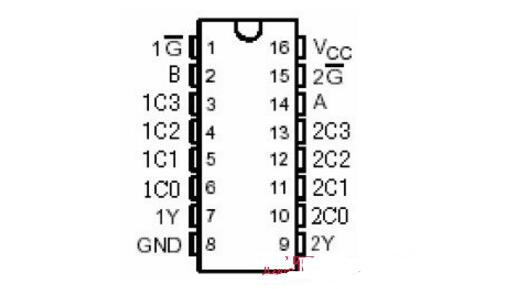

本文介绍了74ls153的管脚图、74ls153功能表、74ls153真值表以及逻辑图,另外还介绍了74ls153封装与74ls153应用电路。

2018-01-26 10:05