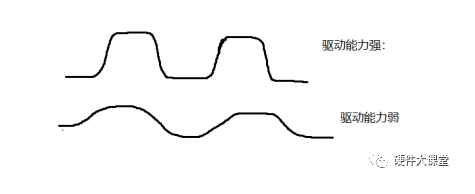

所谓buffer,一般是几级器件尺寸逐步增大的反相器或类似结构的电路,以使得电阻在获得所需的驱动能力时,在功耗延时积上也达到最优。前后级的最佳驱动比例在2.718左右。buffer实际就是两个串联的反相器,常用于时钟路径中,用于增加时钟驱动能力,使得时钟

2023-03-01 13:43

Collapse可以将Sink,ICG,Buffer等cell不展开显示,只以一个简单数字和虚线表示连接关系,下图蓝圈表示该buffer驱动了100个clock sink

2020-05-19 16:20

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock

2022-10-18 18:36

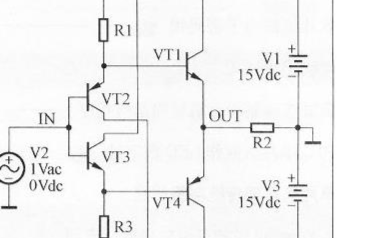

buffer缓冲器电路图与buffer电路示意图 buffer缓冲器的作用 buffer译名为: 缓冲,缓冲器,缓冲液;

2022-10-18 19:01

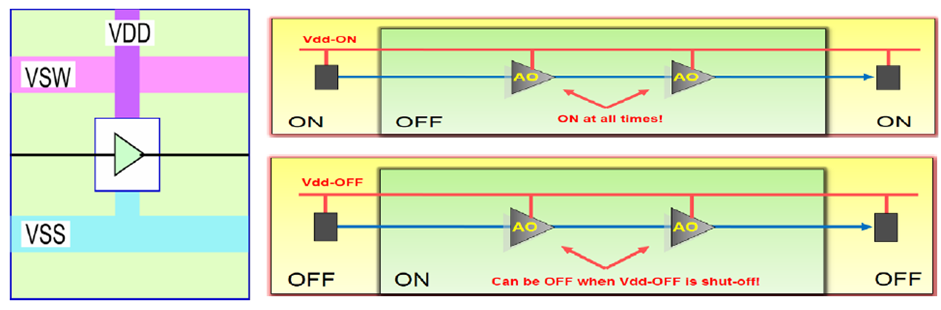

相比普通的buffer cell,always on buffer(AOB)有secondary always on pin,可以让AOB即使在primary power off的情况下保持on的状态;AOB在secondary pg pin off的情况下也是o

2023-12-01 15:31

文章介绍了 BPF ring buffer 解决的问题及背后的设计,并给出了一些代码示例和内核 patch 链接,深度和广度兼备,是学习 ring buffer 的极佳参考。

2022-05-17 09:37

所以 innodb 自己维护了一个 buffer pool,在读取数据的时候,会把数据加载到缓冲池中,这样下次再获取就不需要从磁盘读了,直接访问内存中的 buffer pool 即可。

2023-11-10 16:08

在本篇博文中,我们来聊聊“RQS_CLOCK-12”时钟设置建议以及它如何帮助达成时序收敛。

2023-07-26 09:53

FPGA中的Bank和Clock Region有什么关系?

2023-05-15 09:32

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入

2018-11-12 14:40