在对话框中选择“Specified Objects”,勾选“Placed Standard Cells”然后点击OK。

2022-11-16 10:18

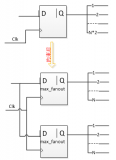

注意get_cells选中的必须是要求编译器复制它来降低扇出的寄存器,因为verilog代码里面和最终实现的电路里面的寄存器名字很可能不一样,所以建议综合完成后在原理图里面去找到对应寄存器,然后复制他的名字,这样就不会弄错。很多时候读者使用命令的时候cells的名

2018-12-27 13:23

在 DRAM Storage Cell 章节中,介绍了单个 Cell 的结构。在本章节中,将介绍 DRAM 中 Cells 的组织方式。

2017-03-17 16:12

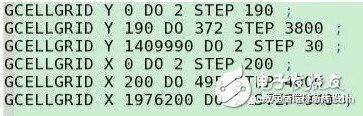

今天我们要介绍的概念是G cell,全称global routing cells。 同样的它也是我们定义的一种grid, G cell grid对routing过程中起着相当重要的作用。

2019-02-02 17:14

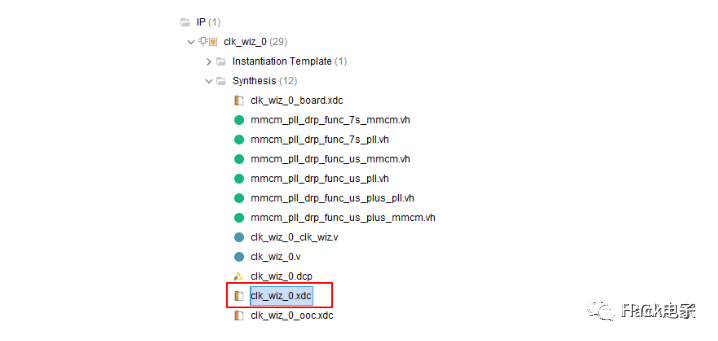

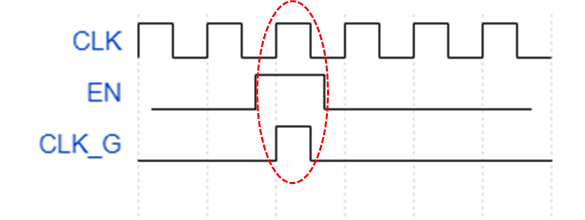

在约束文件XDC(SCOPED_TO_REF、SCOPED_TO_CELLS)中使用“create_clock -name”约束时,在打开综合设计或实现设计时,或者在综合或实现期间,可以观察到以下警告。

2023-12-15 10:10

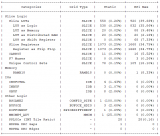

选项-complexity聚焦在设计的资源使用情况,会给出指定RP下各RM的资源使用情况,同时给出各RM之间相比各种资源使用量的最大值,这需要用到选项-cells和-dcps。

2023-11-09 11:22

在约束文件XDC(SCOPED_TO_REF、SCOPED_TO_CELLS)中使用“create_clock -name”约束时,在打开综合设计或实现设计时,或者在综合或实现期间,可以观察到以下警告。

2022-09-02 09:31

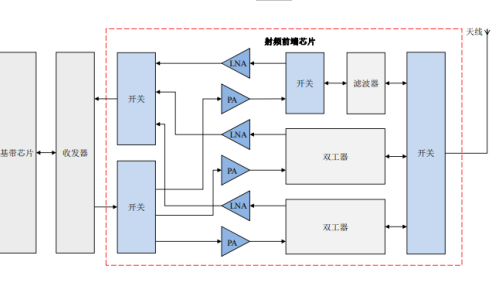

芯片中大部分的动态功耗消耗在时钟网络中。这是由于时钟树上的单元(cells)有较高的翻转率、驱动能力较大且数量较多所导致的。

2023-12-01 14:50

实现高频电光调制,考虑使用横向普克尔效应(EOM、普克尔斯盒、Pockels cells,Conoptics pockels cell EOM),美国Conoptics公司(上海昊量光电国内代理

2015-11-20 16:15

如今,多家电信运营商、基站(Base Station)制造商、小型基站(Small Cells)制造商和用户设备供应商等都在开展5G相关的研发工作。例如,中国(华为)、韩国(三星电子)、日本、欧盟都在投入相当的资源研发5G网络。

2019-02-17 11:46