数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

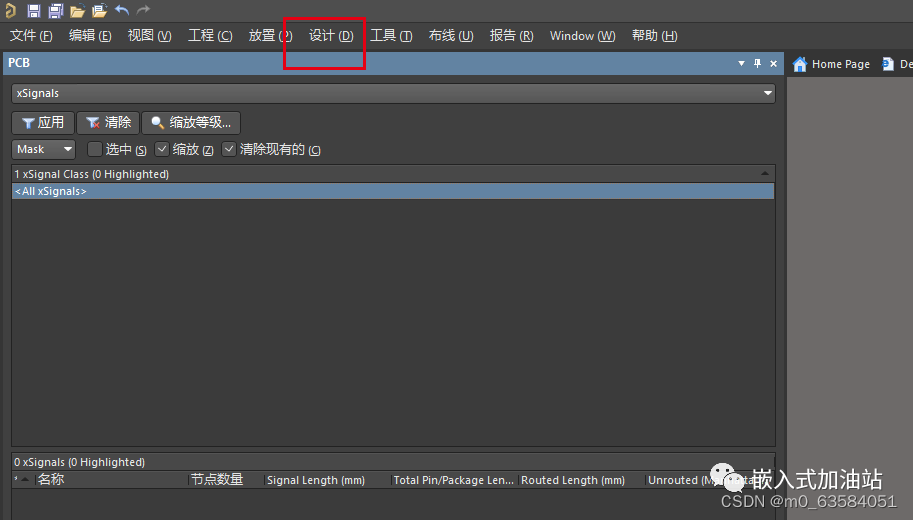

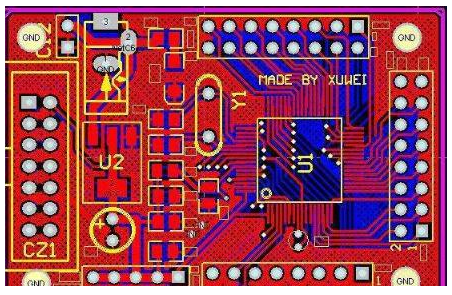

经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。看看下图

2018-11-11 10:55

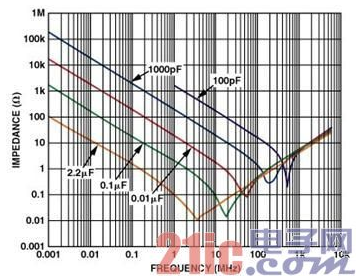

现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑它们之间互相干扰问题,特别是地线上的噪音干扰。

2020-01-22 17:09

当运算放大器工作在很高的射频(RF)频段时,电路的性能很大程度上取决于PCB布线。“图纸”上看起来很好的高性能电路设计,如果由于布线时粗心马虎受到影响,最后只能得到普通的性能。在整个

2019-11-06 16:18

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB设计中,以布线的设计过程限定最高,技巧最细、工作量最大。

2018-03-28 10:31

PCB元器件布局完成后,紧接着就要完成PCB的布线了。PCB布线有单面布线

2019-07-07 09:58

如何优雅的布线呢?布线的方式可以千差万别,为了在布线时避免输入端与输出端的边线相邻平行而产生反射干扰和两相邻布线层互相平行产生寄生耦合等干扰而影响线路的稳定性,甚至在干

2018-07-28 11:01

我们知道,以太网PHY需要通过以太网变压器,RJ45接口与外部设备进行连接,PHY与以太网变压器之间的接口称为MDI接口,也就是介质相关接口(这与MII是相对的)。百兆以太网模式下,MDI是2对差

2019-05-26 09:38

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的, 在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

2020-05-05 15:40