对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

2010-06-28 09:38

为了使二个SDRAM的时钟线等长,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通

2010-06-21 11:57

本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

2019-06-22 09:44

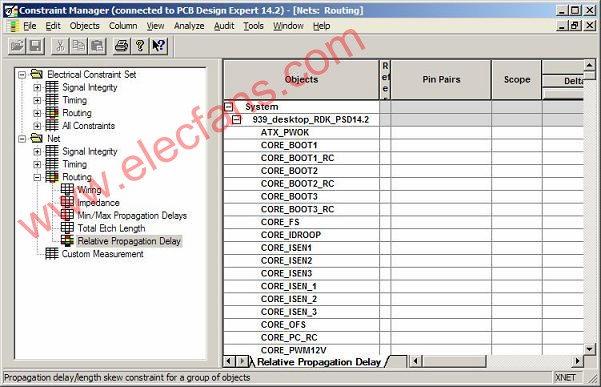

Propagation Delay,如图5-100所示; 图5-100 相对传输延迟设置示意图 第三步,选中一根需要做等长其中一根信

2020-04-15 10:55

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。

2022-11-02 09:25

1.将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要

2018-05-22 10:45

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕

2018-10-19 15:33

如图所示很多用户在进行等长的时候回出现直角或者锐角的等长走线。 那么怎么解决呢: 1)在直接快捷键TR进行蛇形等长的时候,可以按字母键盘上方的数字1 或者2来调整等长走

2020-10-18 09:36

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB 的自动调线功能,将有利于提高设计效率,特别是对于具有较多走线长度要求的设计。

2018-05-15 10:49

上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制。

2018-11-29 15:34