本文为大家带来cadence allegro pcb layout详细教程 。

2018-02-07 11:17

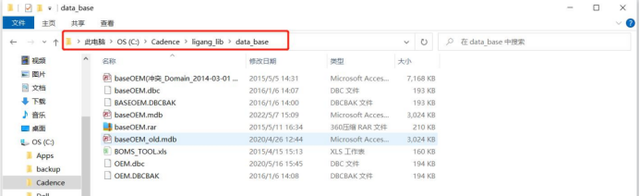

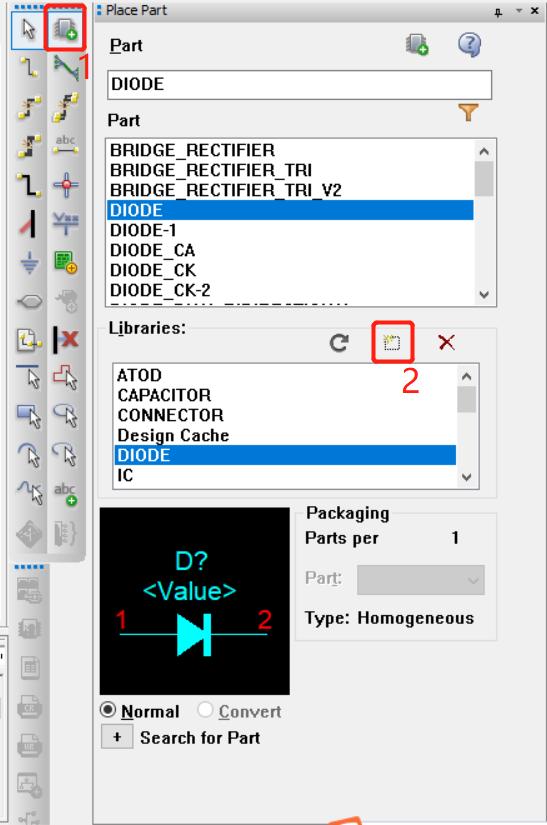

和PCB封装库连接起来,这样才能使原理图封装与PCB封装一一对应起来,保证在导网表时不出现错误。下面笔主就以cadence 16.6为例,详细介绍一下连接到数据库的步骤。

2023-03-27 17:24

Orcad怎么设置复制位号的增加机制,是自动增加还是位号不变呢?

2022-01-26 14:24

针对后期元件装配,特别是手工装配元件,一般都得出PCB的装配图,用于元件放料定位之用,这时丝印位号就显示出其必要性了。

2022-02-15 16:06

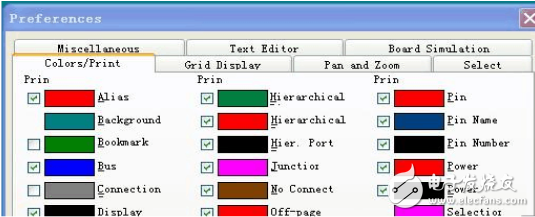

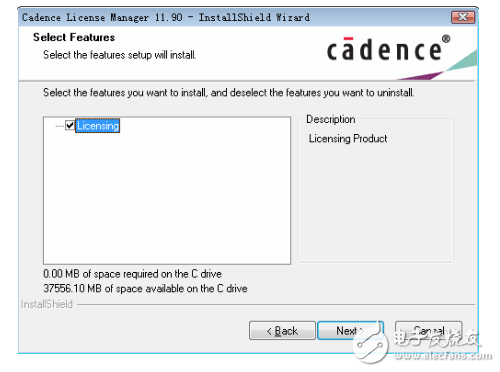

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

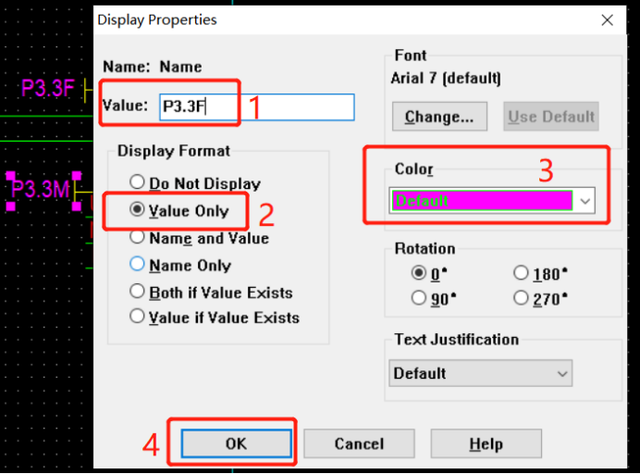

下面笔主就以cadence 16.6为例,详细为大家介绍三种方法,用以批量修改原理图网络名称(这里以将P3.3M网络名称全部改为P3.3F为实例)。

2023-03-27 17:19

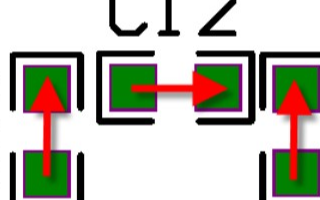

因为位号重排是按照位置来的,所以应在所有元器件位号丝印全部排列好后再进行重排,推荐在出光绘之前进行重排,此时Display -> Status中显示的当前布局布线

2024-04-26 14:11

我们完成 PCB 布局布线后,还需要整理摆放好元件位号和其他的丝印。

2020-10-19 14:37

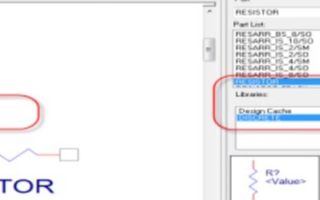

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

由于skill 语言提供编程接口甚至与C 语言的接口,所以可以以Cadence 为平台进行扩展用户,还可以开发自己的基于Cadence 的工具。实际上整个Cadence 软件可以理解为一个搭建在skill语言平台上的

2018-02-07 10:42