Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

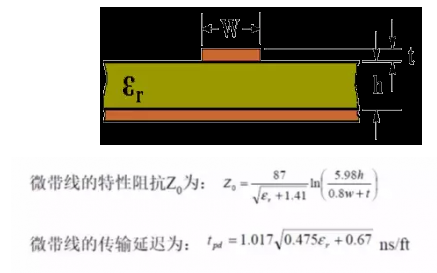

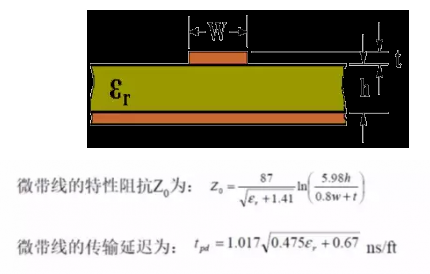

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的

2019-09-06 11:52

CADENCE PCB设计解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,

2011-12-15 14:14

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2018-10-14 09:28

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17

随着现代电子电路信号传输速度的提高,对PCB品质性能的要求也越来越高。PCB提供的电路性能只有起到阻抗匹配,才能使信号在高速传输中保持稳定、无反射、信号完整、无杂讯失真及无噪音等。所以

2022-12-12 14:04

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,

2017-11-26 14:28

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB

2018-05-15 10:49

上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制。

2018-11-29 15:34