VLSI设计的功能验证有两种方法,动态仿真验证和形式验证。形式验证采用数

2022-12-27 15:18

形式验证工具(Formal Verification Tool)是通过数学逻辑的算法来判断硬件设计的功能是否正确,通常有等价性检查(Equivalence Checking)和属性检查(Property Checking)两种方法。

2022-08-25 14:35

今天的形式验证工具具有更大的容量,并且许多工具能够在服务器或云上以分布式模式运行。形式验证的技术和方法也得到了扩展。

2022-11-29 14:31

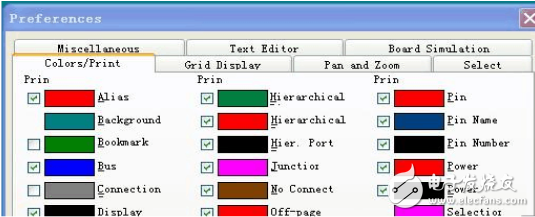

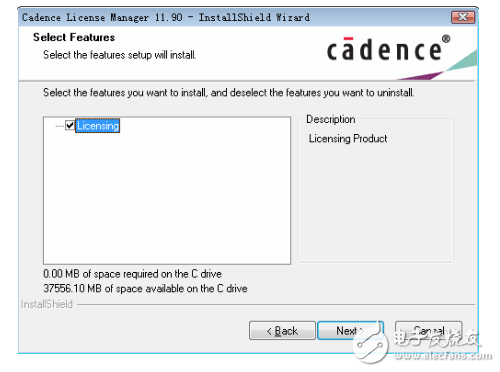

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

RISC-V的开放性允许定制和扩展基于 RISC-V 内核的架构和微架构,以满足特定需求。这种对设计自由的渴望也正在将验证部分的职责转移到不断壮大的开发人员社群。然而,随着越来越多的企业和开发人员转型RISC-V,大家才发现处理器验证绝非易事。

2023-07-10 09:42

在本文中,我们将以西门子EDA处理器验证应用程序为例,结合Codasip L31这款广受欢迎的RISC-V处理器IP提供的特性,来介绍一种利用先进的EDA工具,在实际设计工作中对处理器进行验证的具体方法。

2023-07-10 10:28

本文为大家带来cadence allegro pcb layout详细教程 。

2018-02-07 11:17

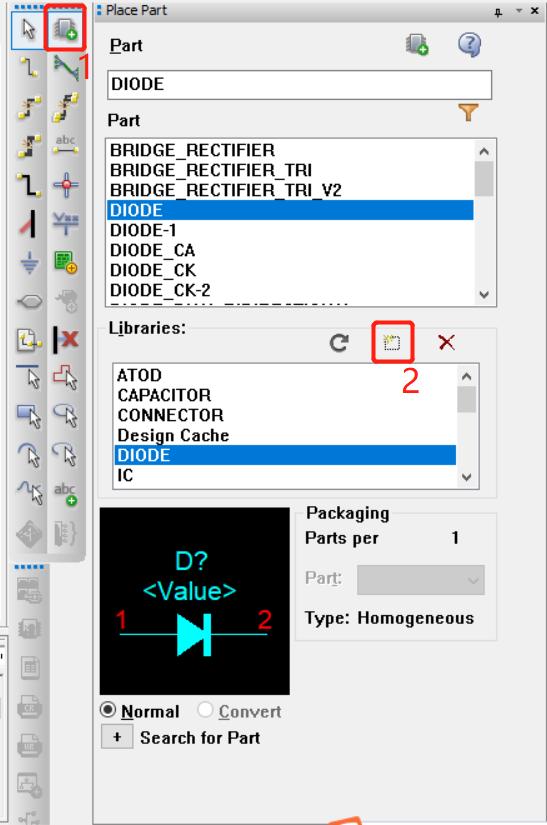

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

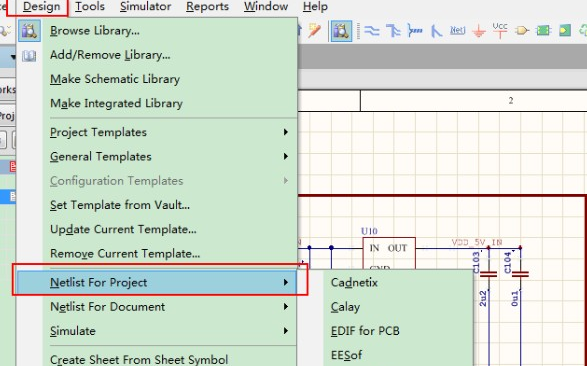

本文,主要描述了,如何使用Altium Desginer 导出Cadence可以使用的网表

2019-10-13 09:15

由于skill 语言提供编程接口甚至与C 语言的接口,所以可以以Cadence 为平台进行扩展用户,还可以开发自己的基于Cadence 的工具。实际上整个Cadence 软件可以理解为一个搭建在skill语言平台上的

2018-02-07 10:42