1 手工添加光绘层 输出光绘的命令在菜单 Manufacture=>Artwork 下或者点击工具栏图标,打开的窗口如下

2018-07-21 11:01

看下图,我在设置top布线层的时候,选择了boundary这个选项中的top,结果就会在电路版中,显示删除孤岛的边界,然后再gerber设置里面,match display,就把boundary/top添加到了top布线层,这样在生成光绘文件,就产生了上面的错误。

2018-04-24 10:45

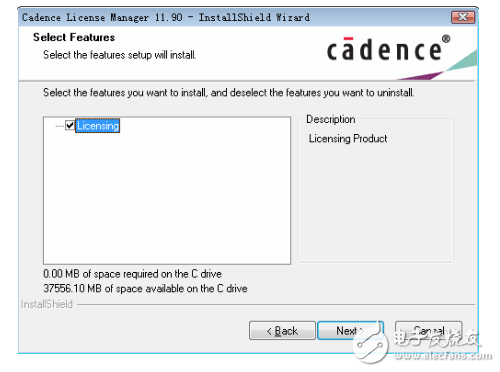

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

后序工艺的不同要求,确定光绘底片(俗称菲林)是否镜像。底片镜像的原则:药膜面(即,胶面)贴药膜面,以减小误差。底片镜像的决定因素:工艺。如果是网印工艺或干膜工艺,则以底片药膜面贴基板铜表面为准

2019-10-14 14:35

在使用cadence进行硬件电子电路设计中,当原理图设计完成之后,下一个步骤就是将设计好的原理图导入PCB中,然后再进行布局和布线;但是在首次进行原理图导入PCB之前,我们需要先将原理图封装库

2023-03-27 17:24

用户在购选激光光绘机前必须检测光绘机的定位精度。用户应该花一段时间去检测光绘机的定位精度及其保持性。激光光

2019-09-13 10:50

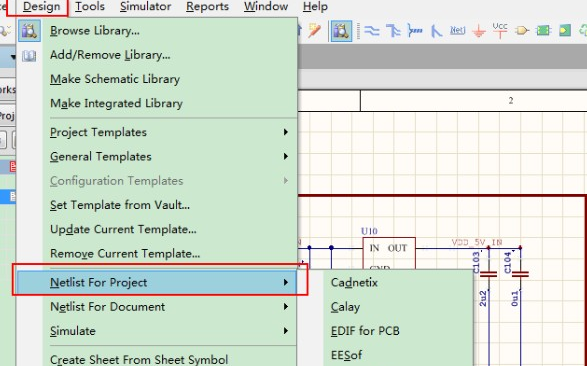

本文,主要描述了,如何使用Altium Desginer 导出Cadence可以使用的网表

2019-10-13 09:15

由于skill 语言提供编程接口甚至与C 语言的接口,所以可以以Cadence 为平台进行扩展用户,还可以开发自己的基于Cadence 的工具。实际上整个Cadence 软件可以理解为一个搭建在skill语言平台上的

2018-02-07 10:42

后序工艺的不同要求,确定光绘底片(俗称菲林)是否镜像。底片镜像的原则:药膜面(即,乳胶面)贴药膜面,以减小误差。底片镜像的决定因素:工艺。如果是网印工艺或干膜工艺,则以底片药膜面贴基板铜表面为准。如果是用重氮片曝光,由于重氮片拷贝时镜像,所以其镜像应为底片药膜面不

2023-08-29 15:09

将电源开关调到“关闭”的状态,在安全光幕安装完成之后,打开电源,给设备供电,安全光幕的指示灯会亮起。

2023-07-15 14:00