Cadence Allegro 22.1-1-3-将网络显示在焊盘、走线、铜皮上

2023-09-25 09:12

在Cadence Allegro16.6版本中,可以很方便的对Shape铜皮进行外扩或者内缩,而不需要重新绘制。

2018-12-02 11:16

比如覆铜间距16mil,其他安全间距8mil,过孔到过孔间距100mil,焊盘到过孔间距100mil,顶层地覆铜0.8mm,顶层VCC3.3与VCC1.8覆铜

2018-12-27 08:46

AD软件提供了某一个元素针对其他元素之间的间距规则的设置。

2024-03-21 09:09

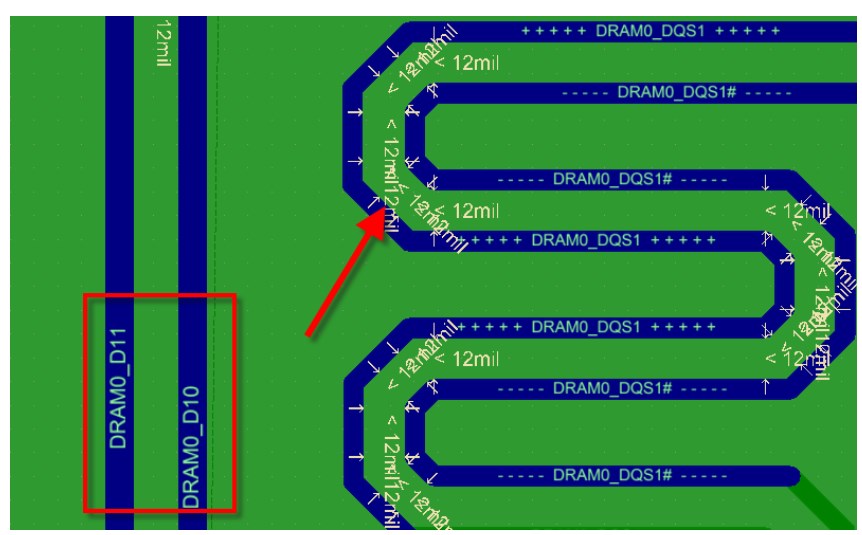

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。

2023-05-30 09:04

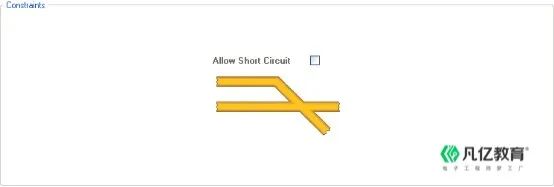

在Altium Designer 9(简称AD9)中设置元器件间距规则,主要是为了确保PCB(Printed Circuit Board,印刷电路板)上的元器件之间保持适当的距离,以避免短路、干扰或

2024-09-02 15:26

在进行PCB设计的过程中,某些焊盘已经铺上铜皮,并且在设计规则中已经设置其与铜皮的连接方式。

2022-11-01 09:36

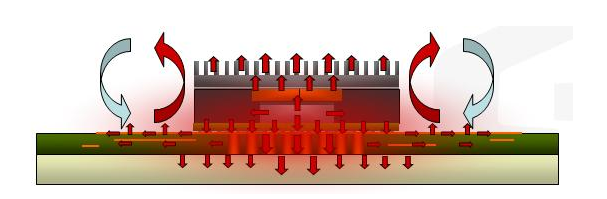

首先给出答案,对于散热,并非铜皮面积越大越好,铜皮较薄时更是如此。

2023-09-21 16:47

实际的应用中,DFN3*3、DFN5*6、SO8等封装类型的贴片元件,都会在PCB板器件位置的底部铺上一大片铜皮,然后器件底部框架的铜皮焊接在PCB的这一大片的铜皮上,加强散热。理论上,PCB板

2023-02-16 11:13

在使用 Altium Designer 进行PCB设计时,除了电气间距(Clearance)等基础规则外, 导线宽度、阻焊层、内电层连接、铜皮敷设等规则也同样重要 。这

2025-04-17 13:54