定位孔用于固定元件的位置,当元件受到外力作用时,定位孔周围的PCB板可能会发生变形或弯曲,进而导致附近走线断裂或元件焊接点开裂。因此,为确保电路板的可靠性,定位孔周围需要设置单边外扩0.5mm的禁布

2025-04-07 17:09

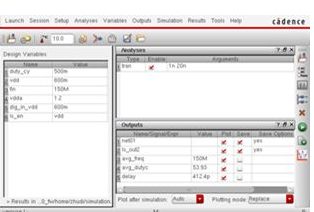

Cadence小技巧有很多,今天就来介绍一种利用lib功能免除新ADE的设置的办法。详细的内容请看文章。

2018-02-18 15:00

请问在Cadence的EMX仿真里,如果需要在一个较长的边打PORT,需要怎么设置会仿真比较精准?像这样子直接吸附一个上去可以吗?

2024-10-23 10:27

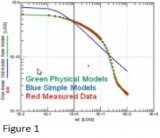

宽禁带材料实现了较当前硅基技术的飞跃。 它们的大带隙导致较高的介电击穿,从而降低了导通电阻(RSP)。 更高的电子饱和速度支持高频设计和工作,降低的漏电流和更好的导热性有助于高温下的工作。 安森美

2020-05-28 09:58

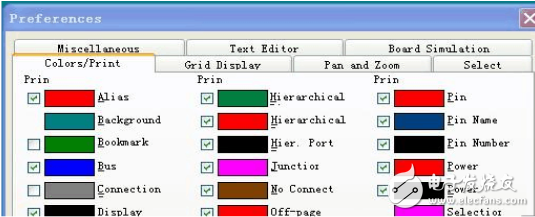

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

其功能可缩短布线时间,并加速产品更早的上市,强大的基于形状的走线推挤功能带来了高生产效率的互联环境,同时可实时地显示长度和时序容限,动态铺铜功能提供了在放置和布线迭代时的实时铺地填充和修复功能,该PCB编辑器还可以产生全套底片加工,裸板装配和测试输出。包括Gerber 274xNC drill和各种格式的裸板测试。

2018-02-07 14:16

本文为大家带来cadence allegro pcb layout详细教程 。

2018-02-07 11:17

功率半导体和宽禁半导体是两种不同类型的半导体材料,它们在电子器件中的应用有着很大的不同。以下是它们之间的一些主要区别: 材料类型:功率半导体通常由硅(Si)或硅碳化物(SiC)等材料制成,而宽禁

2024-07-31 09:07

cadence allegro钻孔图表补充说明 如果在处理钻孔图表的时候,发现没有对不同孔径的钻孔进行标示,可以参考 文章进行调整,也可以利用如下方法, 按照下图设置,就是自动生成钻孔标示

2018-04-14 07:03

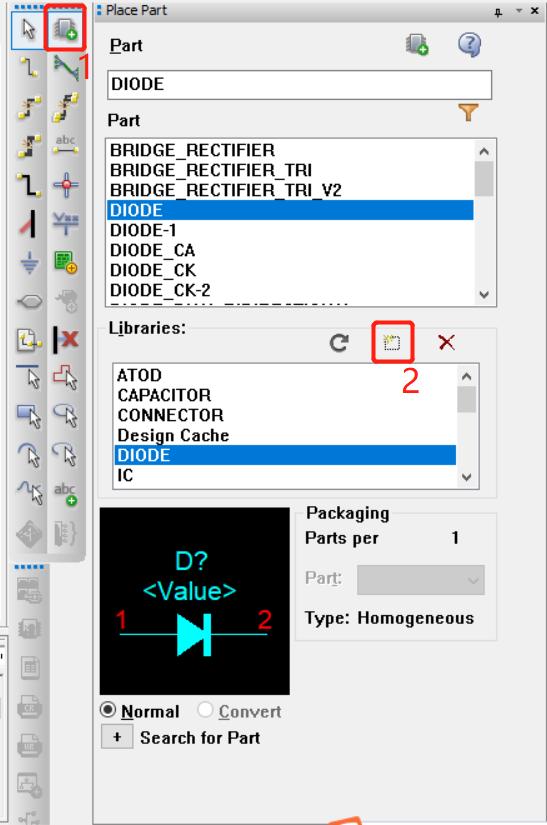

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44