Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、

2018-02-07 17:11

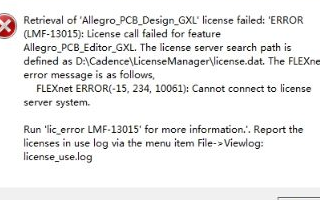

通常情况下,cadence16.X版本破解成功后,不用重启,就能正常运行程序。 但有可能出现重启后,打开cadence时提示找不到license的情况,如下图: 解决方

2019-07-18 09:10

请问在Cadence的EMX仿真里,如果需要在一个较长的边打PORT,需要怎么设置会仿真比较精准?像这样子直接吸附一个上去可以吗?

2024-10-23 10:27

FPGA的前仿真和后仿真在芯片设计和验证过程中扮演着不同的角色,各自具有独特的特点和重要性。

2024-03-15 15:29

sign-off,写出SDF3.0用以后仿真,搭建后仿真的验证环境,添加sc/io/macro的verilog model,仿真输出VCD给Redhawk/Voltus

2024-10-23 09:50

单击快捷图标栏的齿轮图标启动仿真,仿真完毕后,参考前文的前仿真中回波损耗和TDR阻抗曲线图提取方法提取后

2019-02-02 16:32

我们知道芯片上电后,没有POR复位的或者不带复位的寄存器q端要么处于1,要么处于0状态,对于仿真机器而言就是x态。

2024-02-29 10:51

本文章主要详细介绍了pcb版图设计工具,分别有FreePCB、MentorPADS、MentorWG2005。

2019-04-24 17:47

定制化设计工具包含多种内建DRC工具,辅助版图工程师放上多边形。在这些“工具内”DRC检查程序里最著名的是Cadence的DIVA工具,但所有的定制化工具都具备相似的功能,比如SpringSoft的Laker工具有“基于规则的设计”,Synopsys的Custom

2019-09-19 14:29

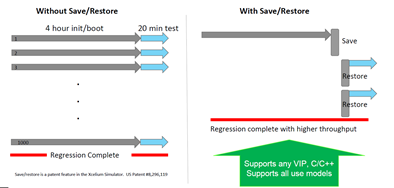

当今片上系统的设计复杂性日益增加,可能导致长达数小时、数天甚至数周的可测试性 (DFT) 仿真设计。由于这些往往发生在专用集成电路(ASIC)项目结束时,当工程变更单(ECO)强制重新运行这些长时间

2023-04-20 10:21