在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与alt

2023-03-26 17:44

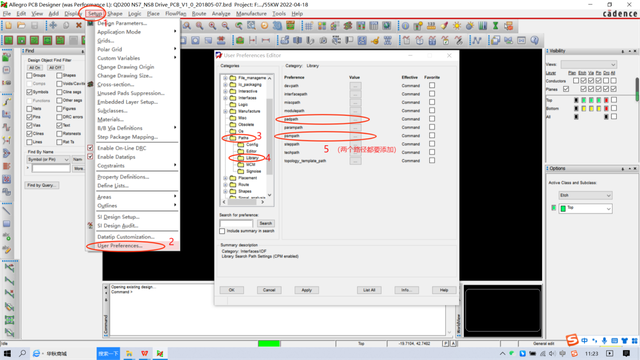

首先打开需要的PCB文件,点击setup→user preferences,在弹出的对话框中选择paths→library→padpath/psmpath(这两个路径都要添加上,否则从原理图导PCB的时候可能会报错)。

2023-03-27 17:21

在使用cadence进行硬件电子电路设计中,当原理图设计完成之后,下一个步骤就是将设计好的原理图导入PCB中,然后再进行布局和布线;但是在首次进行原理图导入PCB之前,我们需要先将原理图封装库

2023-03-27 17:24

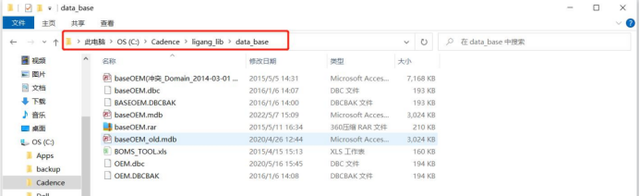

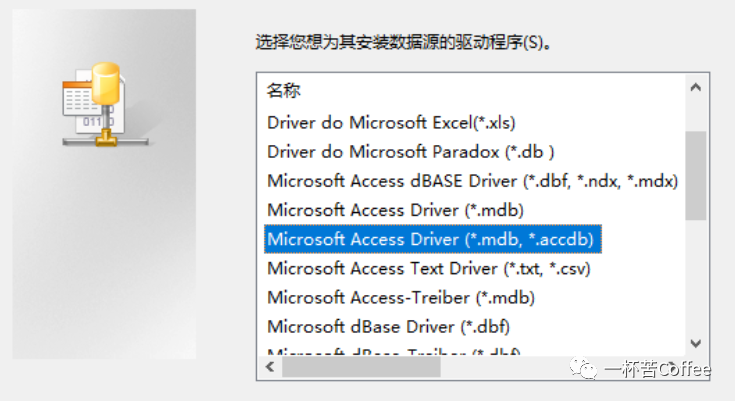

本文将主要介绍Cadence本地库搭建从0到1的过程,并提供搭建过程中所需要的安装软件。搭建Cadence本地库的目的主要是为了方便元器件的搜索与调用。

2023-11-20 17:21

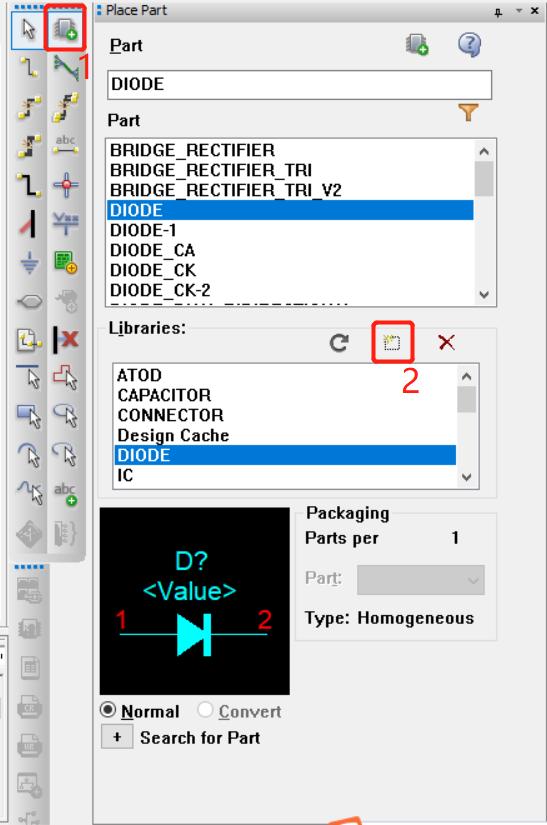

这些库文件的添加需要找到相应功能的库,例如我们要添加模拟量的SCale转换库。首先我们要找到这个的

2022-09-29 16:20

今天为大家介绍一项国家发明专利——一种电能表封印自动加封系统。该专利由国网重庆市电力公司电力科学研究院申请,并于2018年11月27日获得授权公告。

2018-12-21 11:23

库管理非常方便,对接生产采购很容易,画出来的图特别规整。所以大公司都喜欢用Cadence。然后利用PADS弥补Cadence的一些缺点。

2023-04-27 10:38

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

在项目开发过程中,开发者出于保护核心算法的目的,希望将部分核心代码封装起来,使得其他使用者无法查看具体的代码实现细节,而不影响正常的调用。常见的思路是将核心的函数封装成库,下面将结合例程说明具体实现方法。

2020-12-19 09:34

定位孔用于固定元件的位置,当元件受到外力作用时,定位孔周围的PCB板可能会发生变形或弯曲,进而导致附近走线断裂或元件焊接点开裂。因此,为确保电路板的可靠性,定位孔周围需要设置单边外扩0.5mm的禁布区。那么,在封装编辑中,如何为定位孔添加禁布区呢?

2025-04-07 17:09