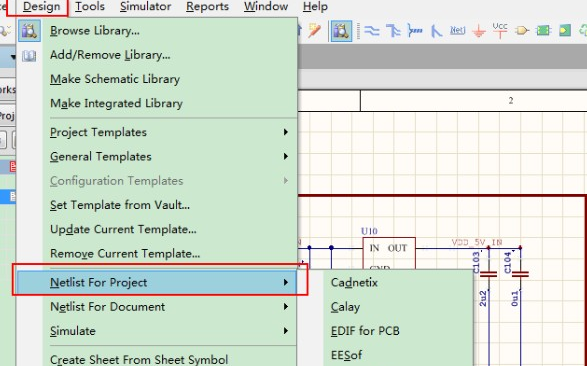

本文,主要描述了,如何使用Altium Desginer 导出Cadence可以使用的网表

2019-10-13 09:15

导通电阻是二极管的重要参数,它是指二极管导通后两段电压与导通电流之比。生活中常用的测量导通电阻的方法有测量接地

2022-01-29 15:49

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

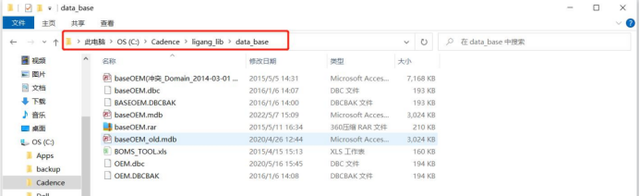

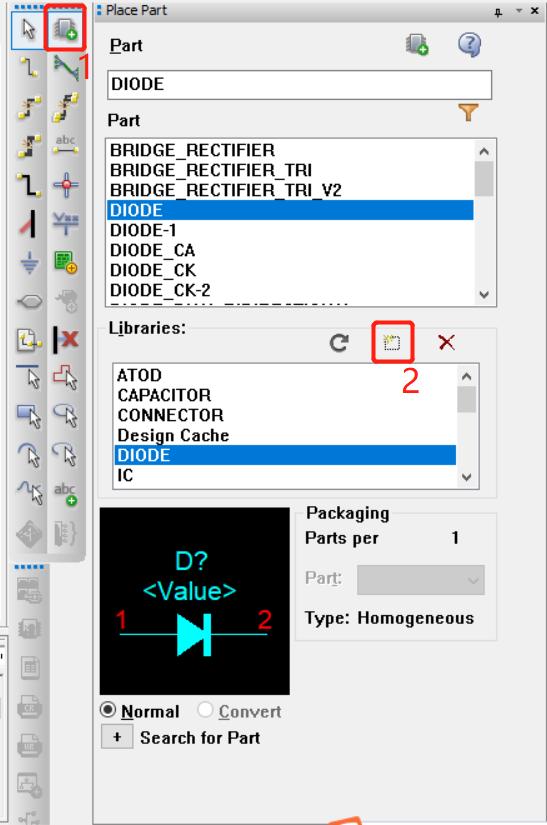

和PCB封装库连接起来,这样才能使原理图封装与PCB封装一一对应起来,保证在导网表时不出现错误。下面笔主就以cadence 16.6为例,详细介绍一下连接到数据库的步骤

2023-03-27 17:24

导磁材料,也称为磁性材料或铁磁性材料,是指那些在外部磁场作用下能够产生显著磁化现象的材料。这些材料在现代科技和工业中有着广泛的应用,包括但不限于电机、发电机、变压器、传感器、磁性存储设备、磁悬浮列车

2024-09-30 11:19

本文为大家带来cadence allegro pcb layout详细教程 。

2018-02-07 11:17

Xilinx ISE使用错误和警告汇总,具体的跟随小编一起来了解一下。

2018-07-13 06:10

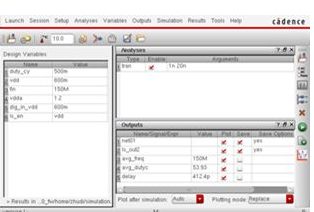

Cadence小技巧有很多,今天就来介绍一种利用lib功能免除新ADE的设置的办法。详细的内容请看文章。

2018-02-18 15:00

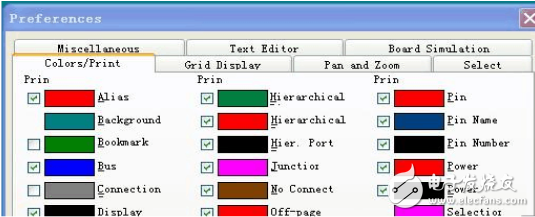

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

Xilinx-vivado的网表形式有edf和dcp两个方式,两个方式各有不同。对于仿真来说,两者均需转换为verilog的形式进行仿真,只是使用的命令不同。

2022-12-20 10:06