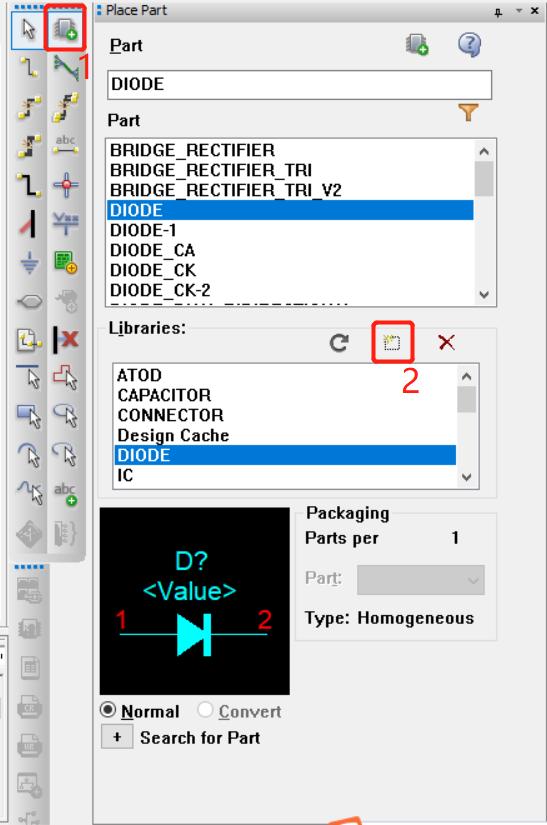

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

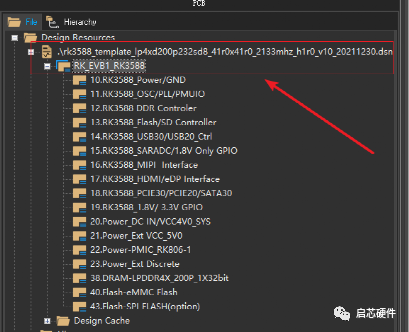

打开Cadence .DSN原理图文件,注意选中整个DSN文件。

2023-10-18 16:07

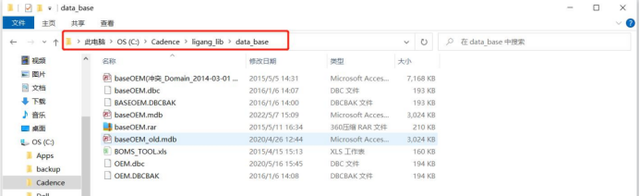

本文通过图文讲解protel99se在win7下安装无法添加原理图库和元件库如何解决,经过小编测试,此解决方法是很有效的。

2013-05-03 23:25

再做一个数字芯片封装的原理图时,希望隐藏电源引脚,但又希望把隐藏的引脚连接到指定的电源网络。 在AD17以及更早的版本中,如图有一个示例:我们隐藏第七个引脚,但是希望自动连接到GND,就可以这样操作了。 之后原理图中的负极网络名称为“

2023-10-16 11:12

PCB线路板吸收热量后,不同材料之间产生不同的膨胀系数而形成内应力,如果树脂与树脂,树脂与铜箔的粘接力不足以抵抗这种内应力将产生分层,这是PCB线路板分层的根本原因,而无铅化之后,装配的温度和时间的延长,更易造成PCB线路板的

2019-04-25 18:11

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

去除原理图背景的网格: OPtions → Display //快捷键O (早期版本在菜单View → Grid )

2024-01-09 14:38

分层起泡区主要集中在控深钻孔区域,且该区域的孔壁铜层厚度不均匀;通过垂直切片,发现L7层附近的孔壁铜厚较薄的位置有微裂纹存在,且裂纹逐渐扩展延伸至L7/L8层芯板的玻纤和树脂界面之间,在外观上形成发白分层现象,说明分层

2019-02-28 10:20

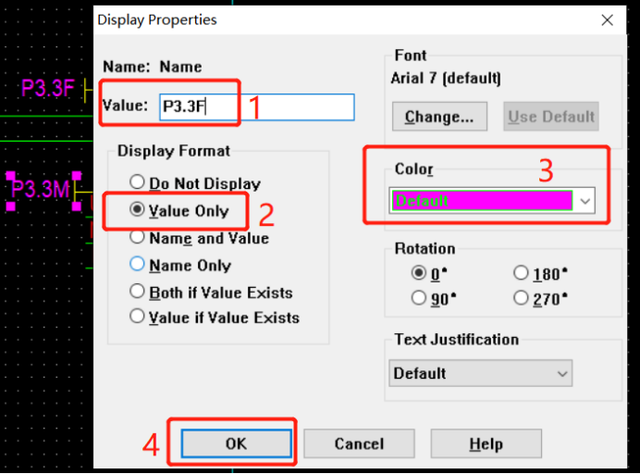

下面笔主就以cadence 16.6为例,详细为大家介绍三种方法,用以批量修改原理图网络名称(这里以将P3.3M网络名称全部改为P3.3F为实例)。

2023-03-27 17:19

在使用cadence进行硬件电子电路设计中,当原理图设计完成之后,下一个步骤就是将设计好的原理图导入PCB中,然后再进行布局和布线;但是在首次进行原理图导入PCB之前,

2023-03-27 17:24