Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

问题:用户无法在Layer Stack Manager中删除层,该选项变为灰色。

2023-12-15 17:13

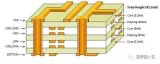

在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;在产品的EMC设计中,除了元器件的选择和电路设计之外,良好的PCB设计也是一个非常重要的因素。

2023-05-30 09:28

CADENCE PCB设计解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,

2011-12-15 14:14

现在很多公司为了降低成本,把目光转向了PCB,比如把原来的六层板改成四层板,在PADS2007中就多出两个无用的层,很多人觉得别扭,总想把它们删掉

2011-11-11 17:48

本文开始阐述了阻焊层的概念,其次对阻焊层的工艺要求和工艺制作进行了详细的阐述,最后解释了pcb阻焊层开窗的概念和PCB阻

2018-03-12 14:23

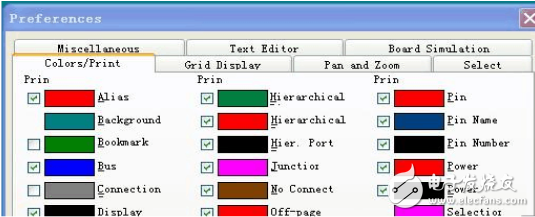

本文为大家带来cadence allegro pcb layout详细教程 。

2018-02-07 11:17

在设计PCB(印制电路板)时,需要考虑的一个最基本的问题就是实现电路要求的功能需要多少个布线层、接地平面和电源平面。而印制电路板的布线层、接地平面和电源平面的层数的确定与电路功能、信号完整性、EMI、EMC、制造成本

2023-06-28 14:27

AD19一次性删除PCB文件的丝印 操作步骤如下: 首先我们解锁我们的器件,只有解锁我们才可以删除掉我们的器件,我们先全选,然后调用panels里面的proprities 解锁操作一下。 现在我们

2020-10-22 09:55

在使用AltuimDesginer (AD) PCB Layout 元件放置层与丝印放置层总是反的, 元件放置在顶层,丝印却在底层, 元件放置在底层,丝印却在顶层

2023-05-16 09:14