Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11

利用原理图和封装生成PCB,首先我们需要将元件的封装一个个的添加进原理图中的元件。

2023-03-02 09:51

更新PCB封装有两种方式,一种是在原理图端更新,然后再导入PCB中; 另一种则是直接在PCB端更新。

2023-03-27 17:18

有时候需要批量修改元件的封装,可在原理图和PCB中批量修改。本文以批量修改电阻AXIAL0.3 的

2019-09-07 09:03

cadence allegro钻孔图表补充说明 如果在处理钻孔图表的时候,发现没有对不同孔径的钻孔进行标示,可以参考 文章进行调整,也可以利用如下方法, 按照下图设置,就是自动生成钻孔标示

2018-04-14 07:03

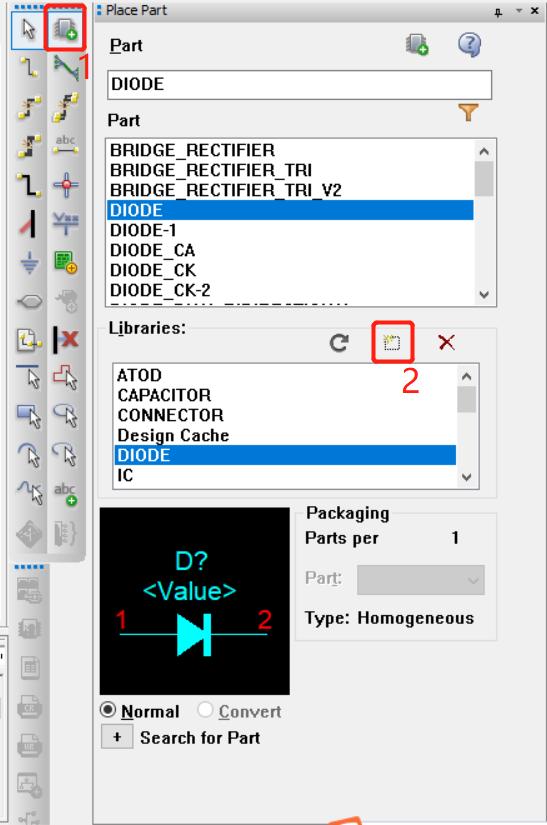

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

CADENCE PCB设计解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,

2011-12-15 14:14

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把

2018-04-05 17:06

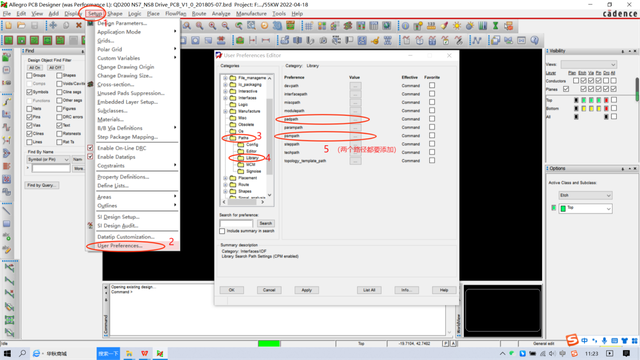

首先打开需要的PCB文件,点击setup→user preferences,在弹出的对话框中选择paths→library→padpath/psmpath(这两个路径都要添加上,否则从原理图导PCB的时候可能会报错)。

2023-03-27 17:21

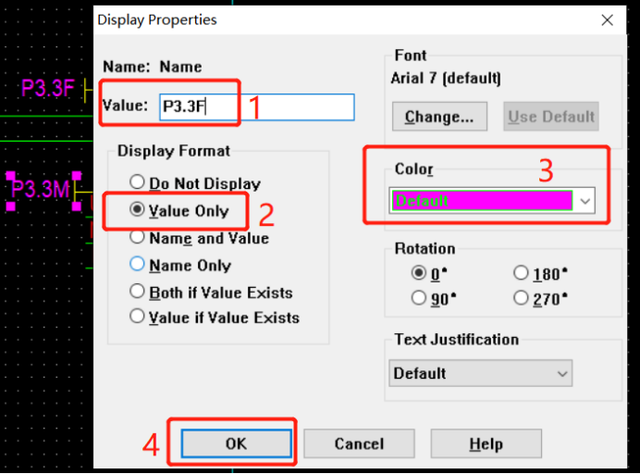

下面笔主就以cadence 16.6为例,详细为大家介绍三种方法,用以批量修改原理图网络名称(这里以将P3.3M网络名称全部改为P3.3F为实例)。

2023-03-27 17:19