如果说TMS320C6678与Kintex-7进行搭配的DSP+FPGA架构堪称经典中的经典,那么TMS320C6678 与ZYNQ进行搭配的DSP+ARM+FPGA架构则为正在崛起的新势力!

2020-12-03 11:56

址的组合,这个值会有所不同。表4列出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上测得的从EDMA触发(写ESR)最小数据传输(1 word)到EDMA 传输结束(读到IPR=1) 的平均的时钟周期数。

2018-02-19 01:11

本白皮书探讨了TMS320C6678处理器的VLFFT演示。通过内置8个固定和浮点DSP内核的TMS320C6678处理器来执行16K-1024K的一维单精度浮点FFT算法样本,检测其分别在采用

2018-01-31 22:58

更详细的讲,cache的结构其实和内存的结构类似,也包含地址和内容,只是cache的内容除了存的数据(data)之外,还包含存的数据的物理内存的地址信息(tag),因为CPU发出的寻址信息都是针对

2019-06-03 14:24

按照数据关系划分:Inclusive/exclusive Cache: 下级Cache包含上级的数据叫inclusive Cache。不包含叫exclusive Cache

2023-05-30 16:02

对cache的掌握,对于Linux工程师(其他的非Linux工程师也一样)写出高效能代码,以及优化Linux系统的性能是至关重要的。简单来说,cache快,内存慢,硬盘更慢。在一个典型的现代CPU中比较接近改进的哈佛结构,c

2022-10-18 09:01

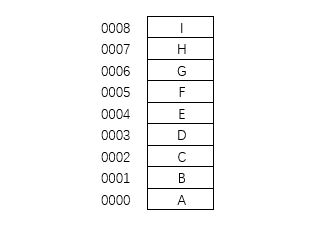

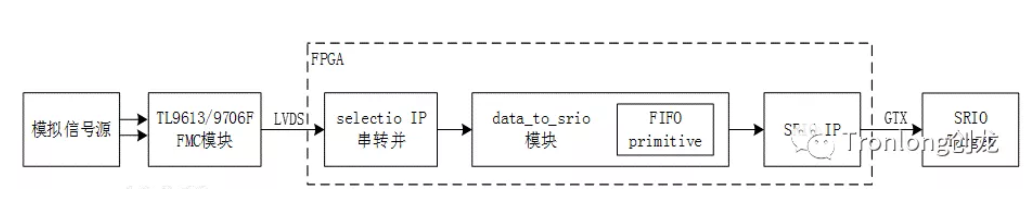

发送,因此数据量为16bit * 2 * 250M = 8Gbps; 2. AD数据通过SRIO由Kintex-7发送到C6678 DSP(Target)的0x0C3F0000~0x0C

2020-06-15 18:18

cpu在执行程序所用的指令和读数据都是针对内存的,也就是从内存中取得的。由于内存读写速度慢,为了提高cpu和内存之间数据交换的速度,在cpu和内存之间增加了cache,它的速度比内存快,但是造价

2018-04-02 10:35

本文开始阐述了CACHE的概念、CACHE替换机构与读写操作,其次介绍了寄存器的原理以及它的主要技术,最后阐述了寄存器和cache两者之间的区别。

2018-04-11 14:10

CACHE 的一致性 Cache的一致性有这么几个层面 1. 一个CPU的icache和dcache的同步问题 2. 多个CPU各自的cache同步问题 3. CPU

2023-06-17 10:38