时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,Viva

2020-11-29 09:41

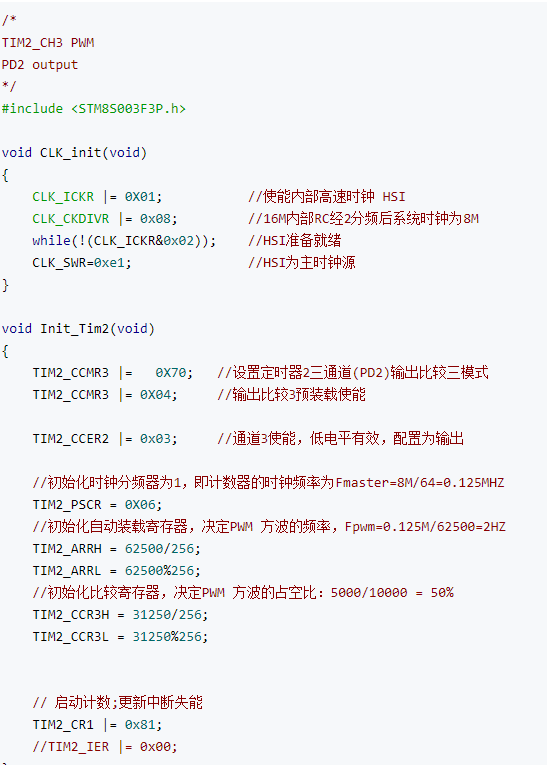

采用STM8S内部时钟(HSI);PWM模式2;占空比为50%,频率为2Hz(方便测试LED灯);PD2口外接LED灯,PD2口输出PWM波;系统时钟初始化很重要:CLK_CKDIVR |= 0x08。

2018-04-16 11:16

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的

2022-10-26 09:04

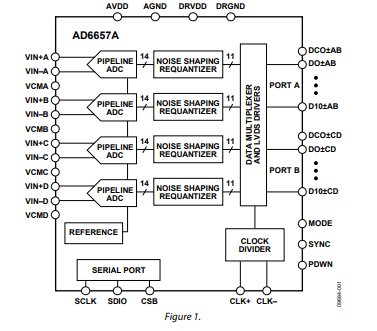

AD6657A是一款11位、200 MSPS、四通道中频(IF)接收机,专为在要求高动态范围性能、低功耗和小尺寸的电信应用中支持多天线系统而设计。 该器件包括四个高性能ADC和NSR数字

2025-04-28 11:25

1. STM32的5个时钟源 a。高速内部时钟 HSI,大约为8MHz b。高速外部时钟 HSE,晶振取值范围在4M--16M,一般采用8M晶振

2018-11-14 16:30

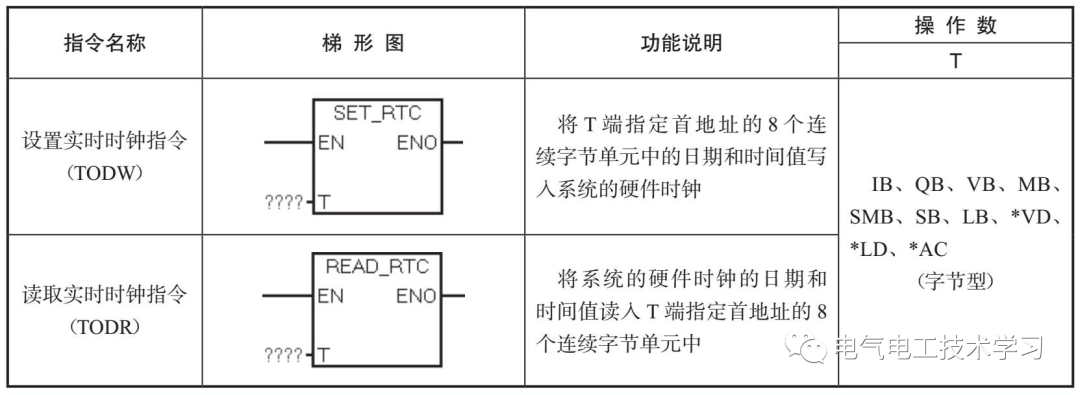

时钟指令的功能是调取系统的实时时钟和设置系统的实时时钟,它包括读取实时时钟指令和设置实时时钟指令(又称写实时

2023-12-13 13:45

STM32的时钟有两个来源——内部时钟和外部时钟。

2017-12-22 09:56

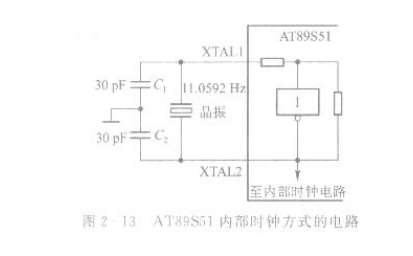

AT89S51内部有一个用于构成振荡器的高增益反相放大器,它的输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体和微调电容,构成一个稳定的自激振荡器,图2-13是AT89S51内部时钟方式的电

2019-05-07 15:50

分享到务来管理时钟节拍,而且采用哈希散列表机制来进一步减少时钟节拍处理过程所花费的时间。本文讨论μC/OS—II在时钟节拍管理方面的不足,并介绍μ

2018-04-09 11:29