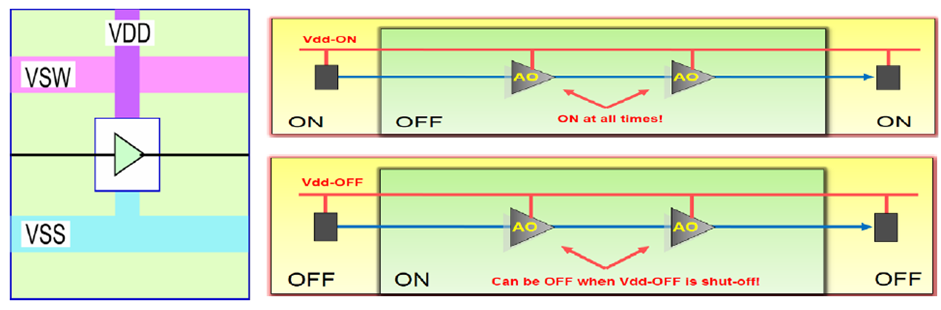

相比普通的buffer cell,always on buffer(AOB)有secondary always on pin,可以让AOB即使在primary power off的情况下保持on的状态;AOB在secondary pg pin off的情况下也是o

2023-12-01 15:31

“always”关键字意味着这个语句块“总是”一直执行。大多数时候“always”后面跟一个边沿事件或者延迟。

2022-12-06 09:47

两者的关系 一个程序块可以有多个initial和always过程块。每个initial和always说明语句在仿真的一开始同时立即开始执行;initial语句只执行一次,而always语句则不断重复

2020-11-24 14:48

1.always@后面内容是敏感变量,always@(*)里面的敏感变量为*,意思是说敏感变量由综合器根据always里面的输入变量自动添加,也就是所有变量都是敏感列表,不用自己考虑。

2022-03-15 14:08

Assign语句和Always语句是在硬件描述语言(HDL)中常用的两种语句,用于对数字电路建模和设计。Assign语句用于连续赋值,而Always语句用于时序逻辑建模。本文将详细探讨这两种语句

2024-02-22 16:24

给设备加入barrier指令支持后,上位机就不再需要通过显式地刷cache来保证请求顺序了。当设备收到barrier指令时,它会确保排在barrier前的所有指令—可能是写也可能是读—都执行完毕、完成数据传输后,才开始执行排在barrier后边的指令。

2019-01-09 18:07

我们再从对可综合代码的支持角度看看SystemVerilog相比于Verilog的优势。针对硬件设计,SystemVerilog引入了三种进程always_ff,always

2023-10-26 10:05

Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在 always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。

2017-02-11 13:17

Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。

2017-02-11 13:28

组合逻辑电路: 可以利用 assign 或者 always @(*) 语句描述。一般复杂的组合逻辑电路利用 always @(*)语句块描述。如上加法器的实现既可以用always语句实现,也可以利用assign语句

2018-09-07 14:47