什么是ALU/3DNow ALU: (Arithmetic Logic Unit,算术逻辑单元)在处理器之中用于计算的那一部分,与其同级的有数据传输单元和分支单元

2010-02-04 11:20

什么是ALU/Brach Pediction ALU: (Arithmetic Logic Unit,算术逻辑单元)在处理器之中用于计算的那一部分,与其同级的有数据传输

2010-02-04 10:51

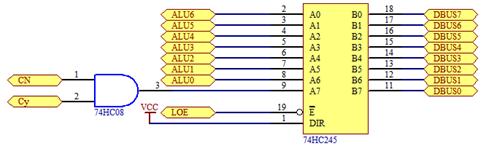

基本要求:设计一个挂在总线上的8位ALU,具有加、减、与、或等功能,要求对运算后的数据能在数码管上面正确显示。在完成基本要求的基础上,可进一步增加功能、提高性能,如增加乘法功能。

2017-06-13 10:55

ALU右移输出原理 直通门将运算器的结果不移位送总线。当X2X1X0=100

2009-04-01 21:08

PICOD-400-ALU - Pushwheel Switches, Subminiature, Panel Mount, Dual Button - Tyco Electronics

2022-11-04 17:22

ALU左移输出原理图 左移门将运算器的结果左移一位送总线。当X2X1X0=110时运算器结果通过左通门送到

2009-04-01 21:06

该ALU采取层次化设计方法,由控制模块、逻辑模块、加减法模块、乘法模块和除法模块组成,能实现32位有符号数和无符号数的加减乘除运算,另外还能实现9种逻辑运算、6种移位运算以

2012-02-09 15:24

`ALU设计1.实验目的ALU(算数逻辑单元)是CPU的基本组成部分。实验要求掌握算术逻辑运算加、减操作原理,验证运算器的组合功能。2.实验准备ALU的基本结构如图2-4-1所示。我们用Robei

2018-08-08 11:08

`本篇教程出自Robei,更多精彩内容请关注RobeiALU设计1.实验目的ALU(算数逻辑单元)是CPU的基本组成部分。实验要求掌握算术逻辑运算加、减操作原理,验证运算器的组合功能。2.实验准备

2015-04-13 15:03

各位大神,最近在做一个软件安全认证的项目,认证公司要求做ALU的检测,个人认为ALU这种最基本的核心单元不会出错,即使出错也自己无法检测,各位有没有相关经历,有没有什么看法呢?大家讨论讨论这样做是否合理啊?

2018-12-03 08:46