Allegro有一个非常好用的打过孔功能,可以在信号线旁边快速打孔,提升了工作效率,避免手动打过孔的烦恼,具体操作步骤如下(本文使用的是Allegro17.4,其他低阶版本使用方法大致相同):点击

2022-10-17 09:38

但是如果只想看SD卡部分原理图,那就需要放大,但是放大时,用滚轮缩放,滚动一下,显示区域过大

2023-01-08 09:03

启动之前安装的License Manager管理器,如图2-17所示,只有添加Cadence官方授权的License文件之后功能才会被激活使用,点击Browse安装,进行License的选择。

2022-08-04 09:03

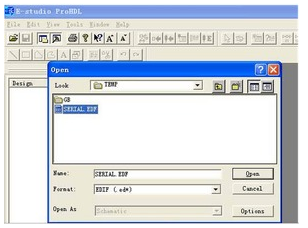

在Protel原理图的转化上我们可以利用Protel DXP SP2的新功能来实现。通过这一功能我们可以直接将Protel的原理图转化到Capture CIS中。

2019-11-28 16:46

系统参数设置窗口用于设置系统整体和各个模块的参数,一般情况下,不需要对整个系统默认参数进行改动设置,只需要对软件的一些常用参数进行设置,比如光标设置,封装库指定等。已达到使软件快速高效地配置资源的目的,从而更高效地使用软件进行电子设计。

2022-09-23 10:32

EDA软件中allegro的模块复用非常实用,可能通常我们的工程师还用的不多,但它在某些场合下还是很有用的,一个是它能减少我们重复性的工作,可以重用的原理图和PCB我们就不需要重复设计了,也就是REUSE。

2018-07-15 10:16

实际绘图过程中会有多种情况发生,例如根据以前的项目做修改应用于新的项目(主要在 PCB 中增加元器件以及添加网络标号进行连线后更新到原理图)下面就来介绍下通过修改 PCB 后更新到原理图的方式方法。

2019-08-19 10:25

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把PCB转成ALLEGRO格式的,然后再用ALLEGRO导出PCB封装

2018-04-05 17:06

1.原理图常见错误: (1)ERC报告管脚没有接入信号: a. 创建封装时给管脚定义了I/O属性; b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上; c. 创建元件时pin方向反向,必须非pin name端连线。

2019-09-11 14:14

电路图,是通过电路元件符号绘制的电子元件连线走向图,它详细的描绘了各个元件的连线和走向,各个引脚的说明,和一些检测数据。

2023-03-31 16:54