相比T拓扑,fly- by在传输较高速率信号时更占优势一些,当然fly-by也并不就是完美的,它自身也存在很多缺陷,例如使用fly-by,负载之间有延时差,导致信号不能同时到达接收端。为解决这个

2016-05-24 14:30

DDR的历史,就是一个SI技术变革的过程,说白了就是拓扑与端接之争。DDR2使用的是T拓扑,发展到DDR3,引入了全新的菊花链—fly-by结构。使用fly-by并不完全因为现在的线路板越来越高

2021-04-11 10:04

信号通道中只要有分叉就会存在阻抗的不连续,fly-by结构处处是分叉,阻抗不连续问题就很突出,到底这种阻抗不连续到了什么程度呢?

2021-04-11 09:58

请问下关于fly-by用在2个SDRAM和1个NandFlash时,下面2个图片结构的作用是否一样?谢谢。第一种情况:第二种情况: 因为看视频只有1个SDRAM的情况,所以想问问2个SDRAM的情况。上面2种情况是不是都可以?是否效果都一样?谢谢。

2019-09-16 10:27

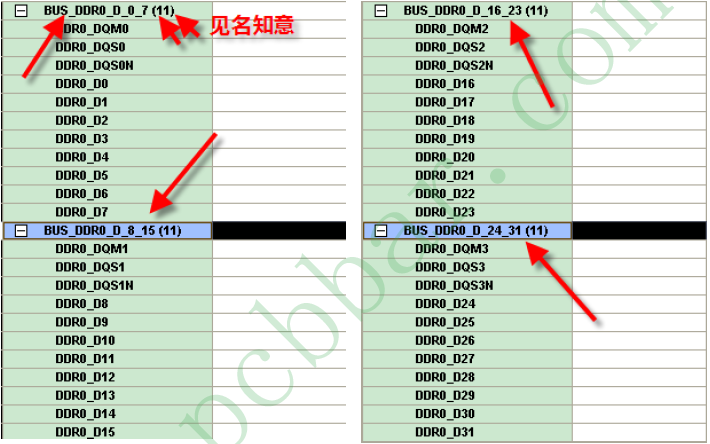

本文档的主要内容详细介绍的是Allegro PCB设计时等长设置的一些方法与技巧解析。以DDR3(4pcs,fly-by 结构)为例,讲述一下在allegro 中如何添

2018-11-27 16:02

分支对信号的影响。以下为仿真结果对比。从仿真结果可以看出,长负载分支的眼高、眼宽小于短负载分支的眼高、眼宽,主要就是由上面提到的负载电容反射造成。 针对DDR3 fly-by的设计,依据在高速PCB领域

2015-11-16 16:04

请教一下DM8148的DDR控制器支持读写平衡吗,没找到描述,用fly-by拓扑,还是T型? 从手册上看应该是fly-by,还想确认一下

2018-05-28 04:33

目前设计过的处理器采用fly-by拓扑当中,基本都是采用RTT通过VTT上拉的方式,但是今天却看到另外一款处理器采用的是RC下拉端接,为什么还有这种操作?原理何在?麻烦知道的大佬帮忙指点指点~~

2018-01-19 16:06

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把PCB转成ALLEGRO格式的,

2018-04-05 17:06

ALLEGRO PCB LIBRARIAN 610AUTOMATED LIBRARY PART CREATION AND VALIDATIONCadence Allegro P

2008-10-16 09:55