在高速PCB中,为实现差分信号等长,且差分对每条线阻抗连续,有时候我们需要对单差分对做特殊调整。 对它的绕线进行补偿,但

2023-03-06 16:44

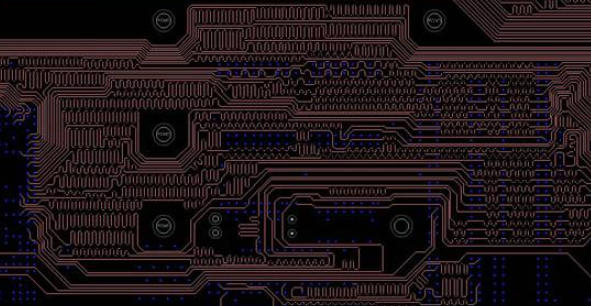

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB

2018-05-15 10:49

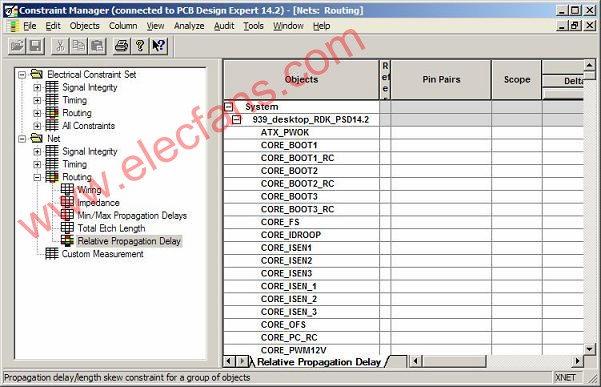

对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

2010-06-28 09:38

PCB设计中常见的走线等长要求

2023-11-24 14:25

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

分线,千兆模式下是4对差分线。在部分PHY芯片的Datasheet或者应用手册中会给出MII/RMM/GMII/RGMII接口,MDI接口的等长规则,但是很少有厂家提到以太网变压器与RJ45之间的差分对

2019-05-26 09:38

1.关于等长 第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。 不知道从什么时候起,绕等长成了一种时尚,也成了

2021-01-20 12:11

等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。 差分信号PCB布线要求 在电路板上,差分走线必须是

2023-02-02 14:33