“锁定”在cache中的块在常规的cache替换操作中不会被替换,但当通过C7控制cache中特定的块时,比如使某特定的块无效时,这些被“锁定”在cache中的块也将受到相应的影响。 用

2023-10-31 11:31

LogicLock逻辑锁定简介 本节介绍Quartus的一个工具LogicLock,会在后面的实例里面介绍LogicLock的具体使用。 逻辑锁定方法学逻辑锁定方法学(LogicLock Methodology

2010-02-08 14:39

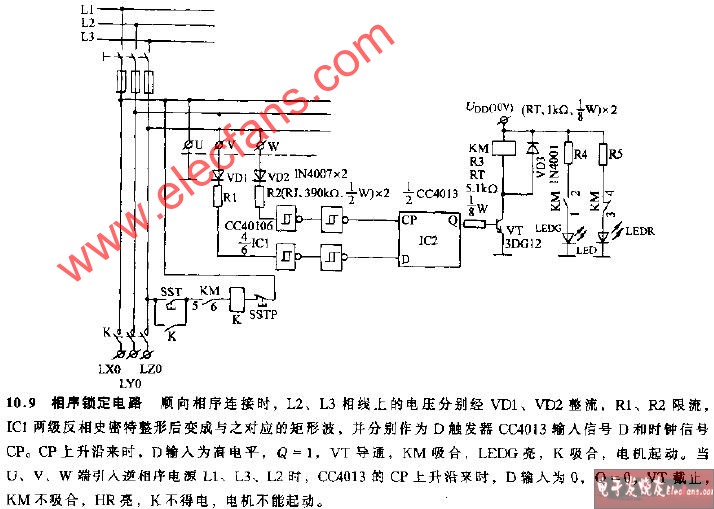

相序锁定电路

2009-02-17 20:28

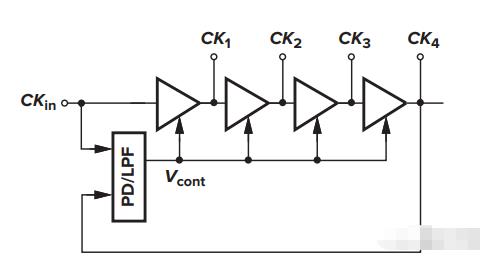

举个简单的例子,假如一个250MHz的DLL,其正常锁定后的整个延时链(VCDL)的总延时为一个周期T,即4ns。但在某些特别情况下,VCDL可能延时2T,即8ns,这就发生了谐波锁定。这时候Loop虽然锁定在一个稳

2023-03-23 14:25

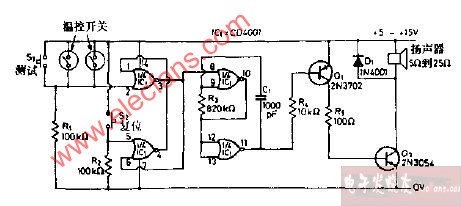

800Hz单音锁定式锁定式火警电路图

2009-06-10 08:57

安川伺服系统是一种广泛应用于工业自动化领域的高性能伺服驱动器和电机系统。在某些情况下,用户可能会遇到伺服参数被锁定的问题,导致无法修改参数。本文将详细介绍如何解除安川伺服参数锁定的方法,以及相关

2024-06-06 12:31

锁相环锁定时间取决于哪些因素?如何加速锁定? 锁相环(PLL)是一种常见的电路,用于稳定频率。PLL中的关键是相锁。相锁发挥着将输入频率与参考频率调整到相等的重要作用。在锁相环设计中,锁定时间是一个

2023-10-30 10:51

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,

2018-05-11 15:14

最近调试有两个问题需要您释疑: 1.9548有频率锁定和相位锁定。两者之间有关系吗?锁定有无先后顺序的要求? 2.在9548频率和相位都锁定之后,9548还是在不停的校

2018-09-05 11:45

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17