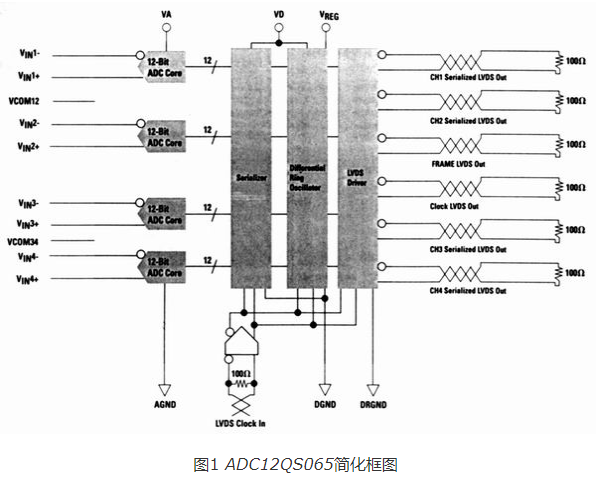

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据

2017-11-17 10:40

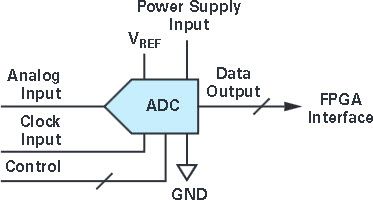

在输入信号转换数字数据之后,必须传输它们到DSP或ASIC/FPGA进行处理。流行的全差分输出信号传输是方便的。全差分的输出信号通过两条对称线给出和吸收电流。这种信号传输的一个例子是LVDS(低压差分信号)格式。

2020-04-04 17:43

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23

本文讨论了标准接口 — SPI、I2C、SPORT、LVDS 和 JESD204A——用于将 FPGA 连接到 ADC。随着数据速率的进一步提高,FPGA与ADC的接口仍将是一个共同的挑战。JESD204B支持12.

2022-12-21 10:57

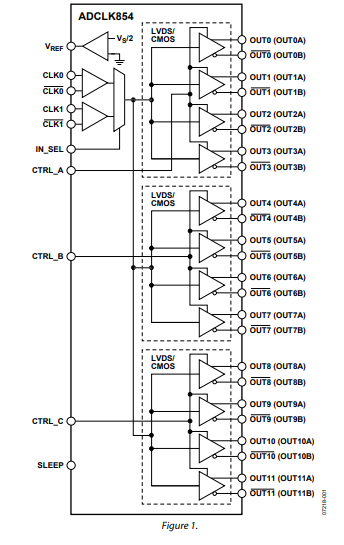

ADCLK854是一款1.2 GHz/250 MHz LVDS/CMOS扇出缓冲器,针对低抖动、低功耗应用进行了优化。其配置范围为12 LVDS至24 CMOS输出,包括LVD

2025-04-11 10:48

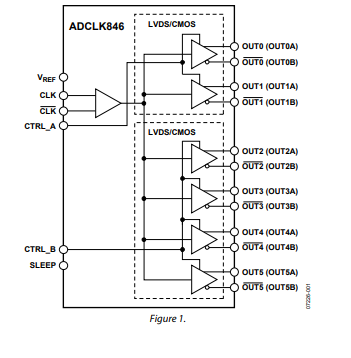

ADCLK846是一款针对低抖动和低功耗优化的1.2 GHz/250 MHz、LVDS/CMOS、扇出缓冲器。可配置范围为6 LVDS至12 CMOS输出,包括LVDS

2025-04-11 10:03

当共模信号较难处理或对系统有负面影响的时候,需要进行信号调理。部分系统的设计会将模拟变换器输出的单端信号转为全差分信号,然后将这些信号传送到差分输入ADC。这种设计的优点是,大部分混入差分线路的噪声会同时出现在两条线路上 (假设差分线路都是按差分方式平衡布局)。

2020-04-12 10:00

什么是LVDS,LVDS的全称是Low-Voltage Differential Signaling ,即低电压差分信号。LVDS可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

2020-11-01 10:03

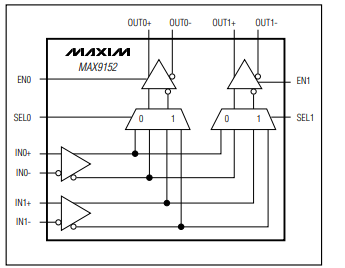

MAX9152 2 x 2交叉点开关专为需要高速、低功耗和低噪声信号分配的应用而设计。该器件包括两路LVDS/LVPECL输入、两路LVDS输出和两路用于设置差分输入和输出

2025-04-16 10:47

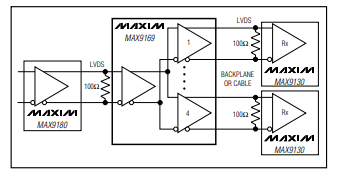

(MAX9169)或LVTTL (MAX9170)输入,将其复现为4路LVDS输出。每路差分输出可驱动100Ω负载,允许在接收器输入端带有100Ω终端电阻的传输线上进行点到点信号分配。MAX9169和MAX9170

2025-05-19 09:30