在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于

2024-11-13 09:49

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为

2019-10-14 16:22

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态内部时钟电路(Clock Circuit)为

2023-02-22 11:11

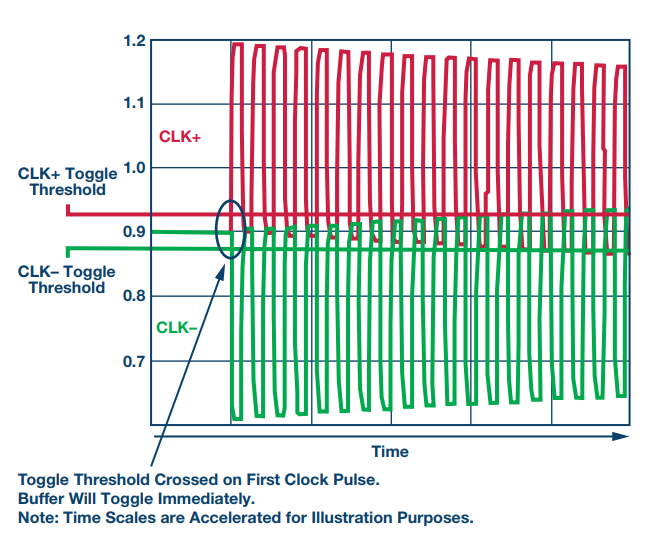

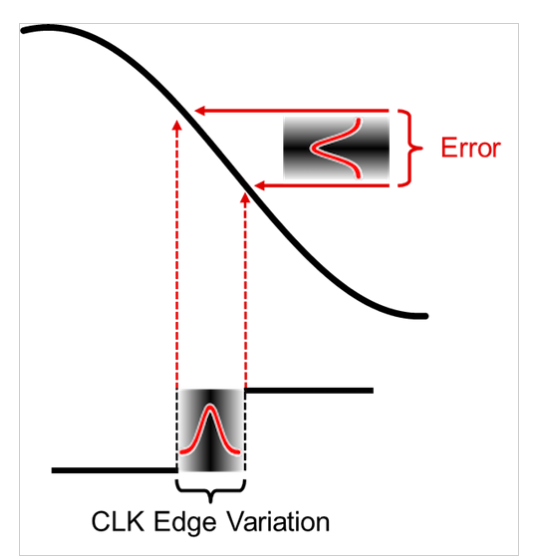

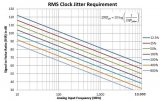

前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容:

2021-04-07 16:43

首先确定ADC 的时钟,这里需要看你的RCC的设置。在采用固件库的基础上,设定ADC的采样频率相对来说是很容易的。由时钟

2017-12-05 09:56

如今大多数ADC芯片里都集成了采样保持功能,以便更好地处理交流信号,这种类型的ADC我们叫做采样

2021-04-28 11:02

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察

2023-01-05 11:07

在 DAQ 系统中,时钟作为时间参考,以便所有组件可以同步运行。对于模数转换器 (ADC),准确且稳定的时钟可确保主机向 ADC 发送命令,并且

2023-03-16 11:14

当ADC时钟输入时,都需要考虑哪些因素呢?如何做才能使ADC充分发挥芯片的性能呢?让ADI公司数字视频处理部高级工程师Ian Beavers告诉你吧! 为了充分发挥

2017-12-19 04:10

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和

2012-03-22 10:45