在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于

2024-11-13 09:49

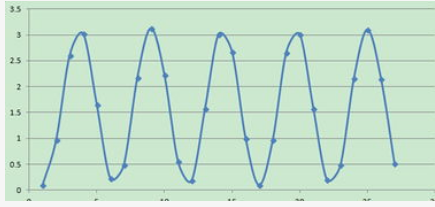

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为

2019-10-14 16:22

本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2017-11-27 14:59

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态内部时钟电路(Clock Circuit)为

2023-02-22 11:11

前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容:

2021-04-07 16:43

最小采样时间为 2.5 个 ADC 时钟周期,最大 ADC 时钟为 80MHz,因此

2022-12-28 06:12

本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24

首先确定ADC 的时钟,这里需要看你的RCC的设置。在采用固件库的基础上,设定ADC的采样频率相对来说是很容易的。由时钟

2017-12-05 09:56

想请问大家: 我拟采用500Msps以上采样率,JESD204B接口的ADC芯片构建2通道以上的一个多通道高速数据采集系统。为使讨论问题具体,简单,明确。现假设有一系统是4个采

2018-07-24 10:45

如今大多数ADC芯片里都集成了采样保持功能,以便更好地处理交流信号,这种类型的ADC我们叫做采样

2021-04-28 11:02