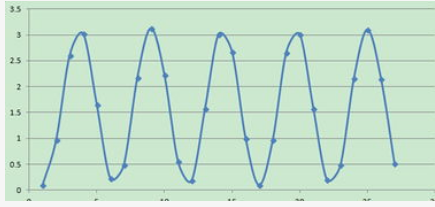

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC时钟

2019-10-14 16:22

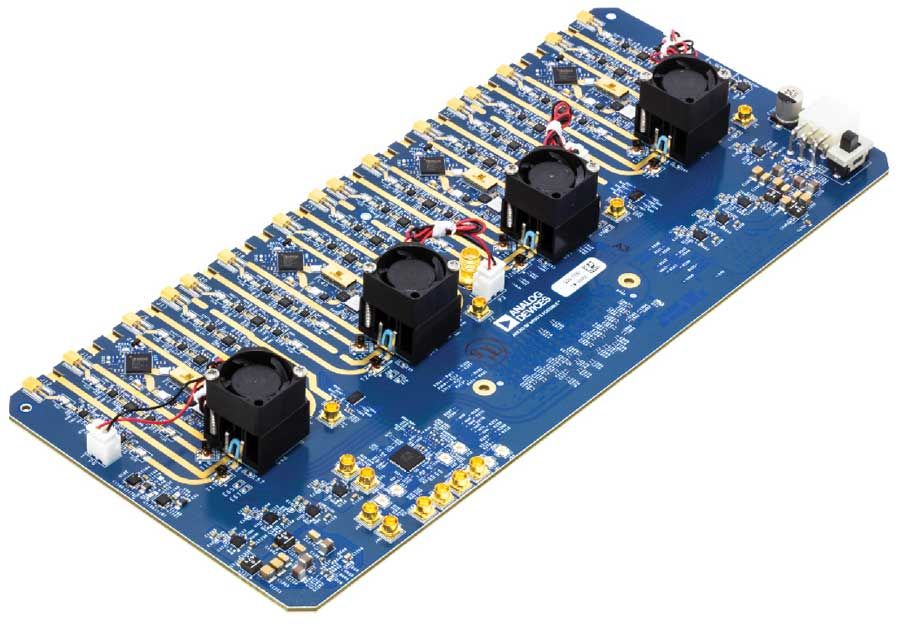

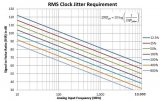

本文详细介绍了 16 通道 S 波段直接采样接收器设计的性能测量与预测。该设计基于最近 发布直接采样模数转换器(ADC),时钟频率为 4 GSPS和转换器第二奈奎斯特区的采样。这 首先使用指向在线参考的指针来描述设计

2022-12-14 13:53

晶振频率是晶体振荡器的固有频率,而时钟频率是以时间为准的振荡频率,一个时钟

2022-01-29 16:57

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,

2023-09-20 14:17

)在单位时间内所出现的脉冲数量多少的计量名称;频率的标准计量单位是Hz(赫)。本文主要介绍什么是时钟频率及编程,具体的跟随小编一起来了解一下。

2018-04-28 09:49

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟

2017-11-18 12:08

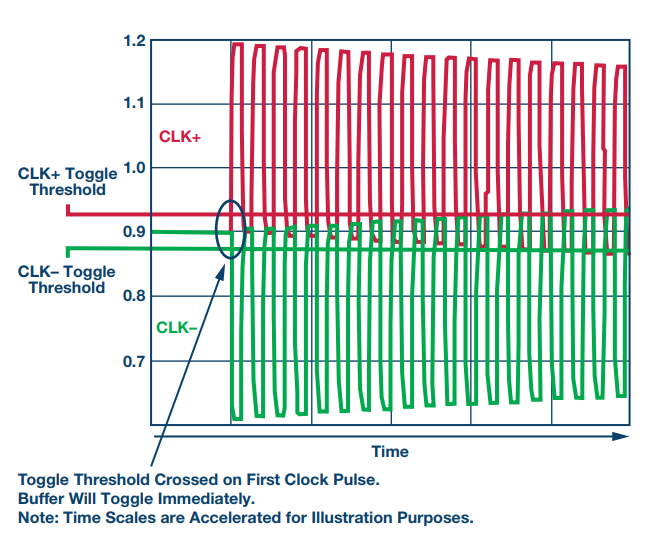

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长

2023-01-05 11:07

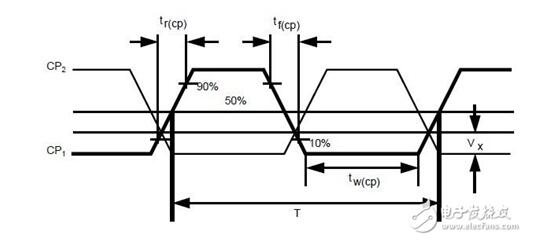

当ADC时钟输入时,都需要考虑哪些因素呢?如何做才能使ADC充分发挥芯片的性能呢?让ADI公司数字视频处理部高级工程师Ian Beavers告诉你吧! 为了充分发挥芯片的性能,应利用一个差分信号驱动

2017-12-19 04:10

在发射端,DS3(E3)时钟和DS1(E1)时钟由输入引脚派生,但DS2(E2)时钟频率是DS3(E3)时钟

2023-02-22 10:10

CPU频率,就是CPU的时钟频率,简单说是CPU运算时的工作的频率(1秒内发生的同步脉冲数)的简称。单位是Hz,它决定计算机的运行速度。本文主要介绍cpu

2018-04-28 10:32