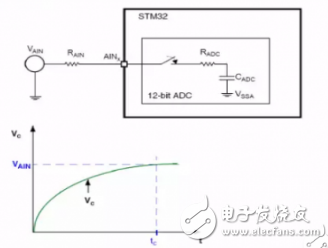

STM32家族中的所有芯片都内置了逐次逼近寄存器型ADC模块.内部大致框架如下: 每次ADC转换先进行采样保持,然后分多步执行比较输出,步数等于ADC的位数,每个ADC

2017-11-29 16:26

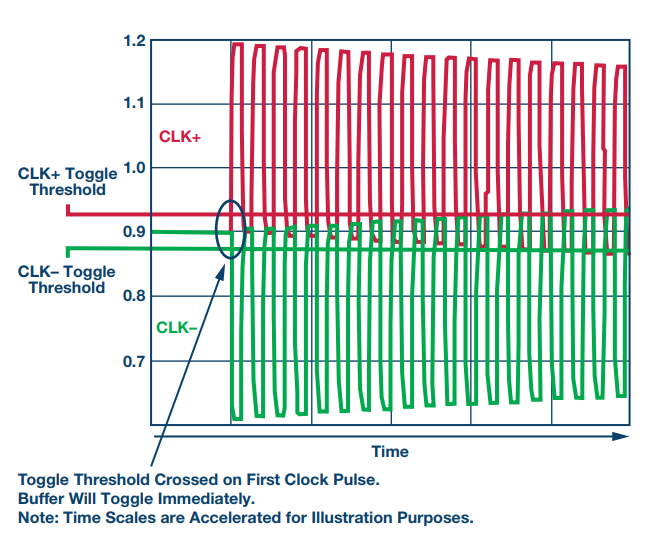

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长

2023-01-05 11:07

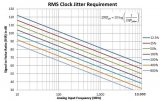

当ADC时钟输入时,都需要考虑哪些因素呢?如何做才能使ADC充分发挥芯片的性能呢?让ADI公司数字视频处理部高级工程师Ian Beavers告诉你吧! 为了充分发挥芯片的性能,应利用一个差分信号驱动

2017-12-19 04:10

在第一篇ADC精度文章中,我们确定了模数转换器 (ADC) 的分辨率和精度间的差异。现在我们深入研究一下对ADC总精度产生影响的因素,通常是指总不可调整误差 (TUE)

2018-07-10 17:54

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC时钟频率为:71.4 /(6

2019-10-14 16:22

随着使用多模数转换器(ADC)的高速信号采集应用的复杂性提高,每个转换器互补时钟解决方案将决定动态范围和系统的潜在能力。 随着新兴每秒一千兆样本(GSPS) ADC的采样速率和输入带宽提高,系统

2018-02-11 05:44

当ADC交错时,使用两个或多个具有定义时钟关系的ADC同时对输入信号进行采样,并产生组合输出信号,从而在单个ADC的某个

2022-12-21 11:46

SPICE是一种用于模拟和分析电子电路的计算机程序。在SPICE仿真中,产生时钟信号是许多电路设计和模拟任务中的关键步骤。

2024-02-06 14:22

执行,ADC转换的结果可以左对齐或右对齐储存在16位数据寄存器中。ADC的输入时钟不得超过14MHz,其时钟频率由PCLK2分频

2023-02-10 14:57

ADC B通道提供采样时钟。这两个时钟的关系是由同一个外部时钟源产生时钟

2023-02-22 11:11