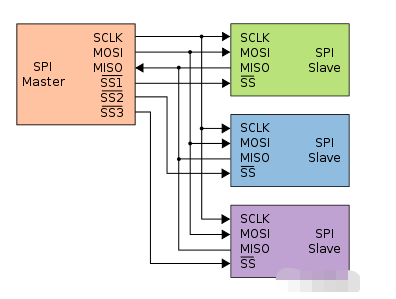

之前用STM32的SPI需要控制很多外部芯片,可是一个SPI的外设只有一个片选,要实现独立片选一主多从,怎么实现呢?

2023-01-20 11:53

ADAR5000 是一款 1:4 Wilkinson 功率分配器,专为对空间敏感的微波信号分配应用而设计。在 17GHz 至 32GHz 频率下,额外插入损耗范围为 −1.5dB 至 −2.5dB

2025-04-08 17:20

ADAR5001 是一款 1 对 2 的 Wilkinson 功率分配器,其设计 适用于空间受限的微波信号分配应用。 额外插入损耗范围为 −1.0 dB(从 10 GHz 到 18 GHz GHz

2025-04-08 17:05

本文基于MBIST的一般测试方法来对多片SRAM的可测试设计进行优化,提出了一种通过一个MBIST控制逻辑来实现多片SRAM的MBIST测试的优化方法。

2011-12-15 10:25

ADAR1000 是一款适用于相控阵的 4 通道 X 和 Ku 频段波束形成内核芯片。此器件在接收和发射模式之间以半双工状态工作。在接收模式下,输入信号通过四个接收通道后在公共 RF_IO 引脚

2025-04-08 18:09

大家如果做过DDR的设计可能会发现在进行多片DDR连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?

2023-12-18 15:58

当将SoC的代码分割到多片FPGA的任务完成,并且所有FPGA的资源利用都很平衡,在建议的范围50%到70%左右。此外,每个FPGA中被分配到的RTL设计的IO最小化,也就是说分割

2023-05-23 09:40

多路同步数字调相信号源一般采用单片机和多片专用DDS芯片配合实现。该技术同步实现复杂,成本高。给出了一种基于FPGA的多路同

2016-05-27 13:47

的光。因此,在选择合适的滤光片时需要考虑传感器的灵敏度。 下文将通过示例介绍不同类型的滤光片,并详细解释滤光片的原理。其他示例包括使用滤光片的实际应用,例如智能交通系统(ITS)、机器视觉和检测、精准农业和

2023-06-16 14:17

随着测试环境越来越复杂,需要采集的参数种类越来越多,要求采集系统连续采集各种传感器输出的模拟信号,而目前常用的固态存储器件FLASH的写入速率比较低。本文提出一种基于FPGA(现场可编程门阵列)片

2018-07-12 09:06