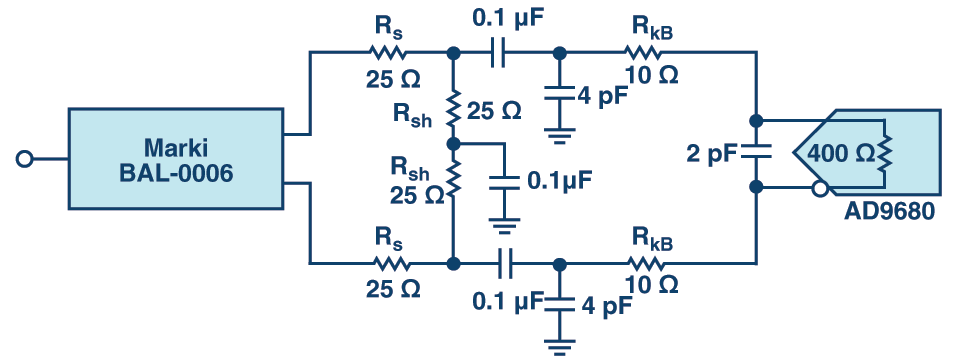

通常,ADC(模数转换器)性能额定为–1 dBFS。一些数据手册规定失真低于满量程0.5 dB。无论是低于满量程1 dB还是0.5 dB,这样做都是为了防止在满量程(0 dBFS)下运行ADC输入时信号削波。台式RF信号发生器通常以dBm为单位输出信号。为了在1.1 V p-p满量程ADC上实现–7 dBFS,只需要7.6 dBm信号电平(基于50 Ω的基准阻抗)。但是,当您这样做时,ADC的单音FFT输出显示–6.7 dBFS。有人吃掉了所有的分贝吗?

2023-02-01 11:35

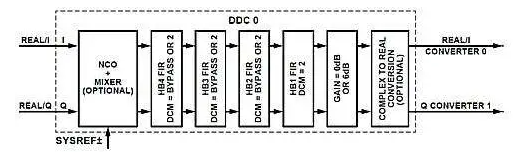

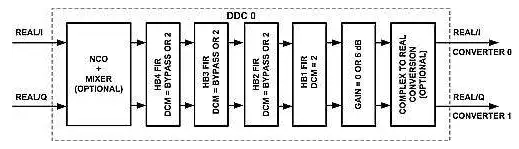

在本例中,我们将介绍AD9680-500,其工作输入时钟为368.64 MHz,模拟输入频率为270 MHz。首先,了解AD9680中数字处理模块的设置非常重要。AD9680将设置为使用数字下变频

2023-06-30 15:46

MAX9680高速放大器和滤波器优化用于便携式视频系统。器件经过专门设计,兼容于嵌入至应用处理器内、具有0.4VP-P视频输出的视频编码器。输入共模范围包含GND电位,允许视频

2010-12-20 09:34

ADI和Arrow推出采用Arria 10 GX、AD9144和AD9680的双通道1GSPS数据采集套件。该套件使用开源系统设计,用于在HDL、软件和模型设计环境中演示DSP算法。

2018-06-07 02:46

在本例中,我们将介绍AD9680-500,其工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680将设置为使用数字下变频器(DDC),具有实际输入、复数输出、155

2023-06-30 15:20

回想一下示例中,AD9680-500的工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680设置为使用数字下变频器(DDC),具有实输入、复数输出、155 MHzNCO

2023-06-30 15:18

在本文的第一部分“数字下变频器——第1部分”中,我们探讨了行业对更高频率RF频段采样的推动,以及数字下变频器(DDC)如何实现这种类型的无线电架构。讨论了与AD9680系列产品中的DDC相关的几个技术方面。

2023-01-05 14:28

CMOS电路功耗主要由动态功耗和静态功耗组成,动态功耗又分为开关功耗、短路功耗

2024-04-01 16:16

AD9680 ,它具有同类产品中的最佳噪声和动态范围性能,支持通讯、仪器仪表和军事/航空航天领域的直接RF采样应用。

2014-05-16 10:59

双通道接收+双通道发射FMC模块满足VITA57.1单宽、导冷规范。模块ADC支持国产GM4680/B9680或进口AD6674-500、AD6674-750、AD6674-1000

2023-08-14 21:50