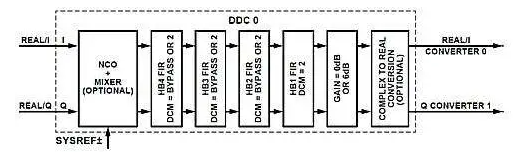

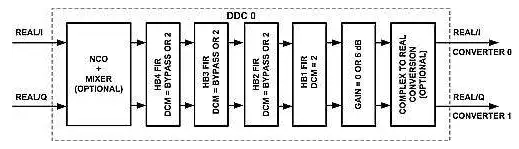

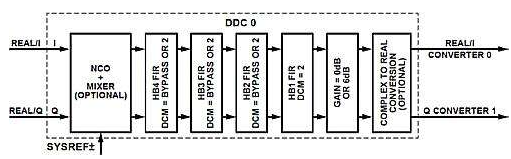

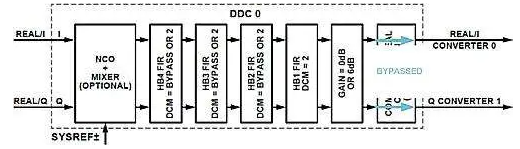

在本例中,我们将介绍AD9680-500,其工作输入时钟为368.64 MHz,模拟输入频率为270 MHz。首先,了解AD9680中数字处理模块的设置非常重要。AD9680将设置为使用数字下变频

2023-06-30 15:46

在本例中,我们将介绍AD9680-500,其工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680将设置为使用数字下变频器(DDC),具有实际输入、复数输出、155

2023-06-30 15:20

回想一下示例中,AD9680-500的工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680设置为使用数字下变频器(DDC),具有实输入、复数输出、155 MHzNCO

2023-06-30 15:18

在本文的第一部分“数字下变频器——第1部分”中,我们探讨了行业对更高频率RF频段采样的推动,以及数字下变频器(DDC)如何实现这种类型的无线电架构。讨论了与AD9680系列产品中的DDC相关的几个技术方面。

2023-01-05 14:28

作者:任凯 蓝牙技术联盟开发者关系高级经理 LE Audio是下一代蓝牙音频,它基于低功耗蓝牙(LE)工作,而Classic Audio则基于经典蓝牙射频(也被称为蓝牙BR/EDR射频)工作

2020-03-18 09:05

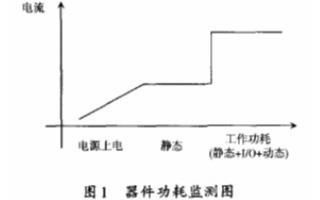

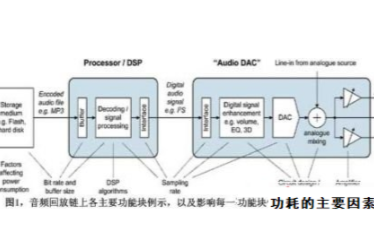

功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低

2021-02-14 17:50

我们将再次以AD9680为例。在这种情况下,无论速度等级如何,归一化抽取滤波器响应都是相同的。抽取滤波器响应仅随采样速率成比例。在此包含的示例滤波器响应图中,没有准确给出具体的插入损耗与频率的关系

2023-06-30 15:43

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机功耗,是指逻辑门没有开关活动时的功率消耗,主要是由晶体管的漏

2020-01-16 09:46

我们将继续以AD9680为例,就像在第1部分中所做的那样。与DDC的实际模式操作类似,无论速度等级如何,归一化抽取滤波器响应都是相同的。我想再次提到,对于此处包含的示例滤波器响应图,没有准确给出

2023-06-30 15:44

功耗是需要考虑的重要因素之一,对于功耗,我们应当给予一定的关注。在往期功耗相关文章中,小编对FPGA低功耗设计有所介绍。为帮助大家对

2020-12-12 09:08