AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)

2025-04-11 09:37

ADI 公司的AD9547是双路/四路输入网络时钟发生器/同步器,能为许多系统包括同步光网络(SONET/SDH)提供同步.输入基准频率从1 kHz 到750 MHz,频率监视1ppm,输出频率高达450MHz,主要

2010-02-14 10:14

AD9547 具有高出66%的抖动性能、100倍的更窄回路滤波器带宽的时钟器件 AD9552能够替代包括OCXO(恒温

2009-09-01 17:28

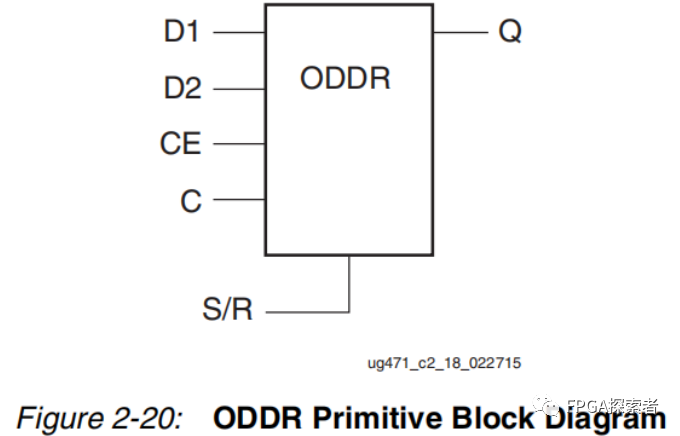

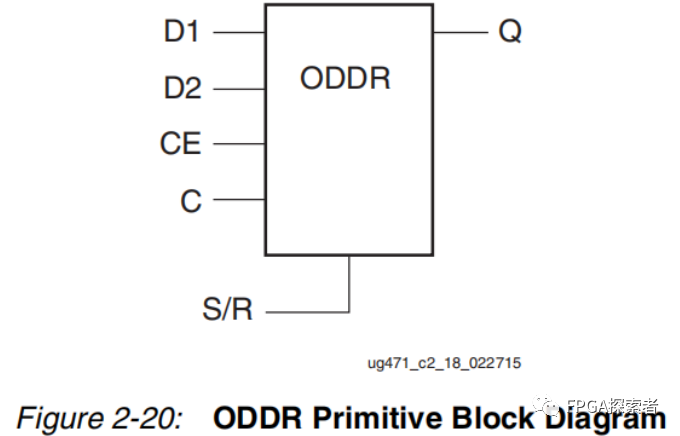

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑,连接方式:输出

2023-06-21 14:11

MAX9489/MAX9471多输出时钟发生器构建集成时钟源 摘要:与典型的“本地”时钟方案相比,集成的多输出

2008-10-04 20:43

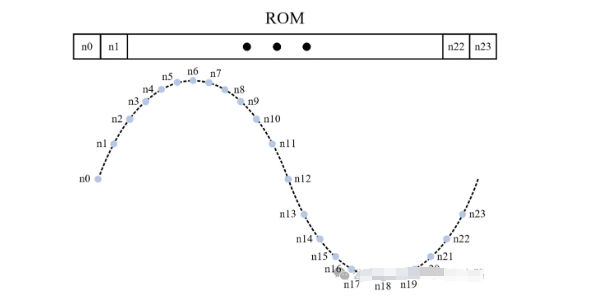

DDS(Direct Digital Synthesizer,直接数字频率合成器)技术是一种频率合成方法,其输出频率与时钟之间存在密切的关系。 一、DDS基本原理 DDS技术通过编程频率控制字来分频

2024-10-06 15:27

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑

2023-06-27 10:21

在FPGA的源同步的系统设计中,常常我们会碰到把随路时钟和数据一同输出的情形,如同下面的系统: 在这样的系统中,要求输出时钟o_clk和o_dat要由严格的相位对齐关系

2019-10-12 17:59

一、主时钟create_clock 1.1 定义 主时钟是来自FPGA芯片外部的时钟,通过时钟输入端口或高速收发器GT的输出

2024-11-29 11:03

MAX3679A高性能四路输出时钟发生器(Maxim) Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51